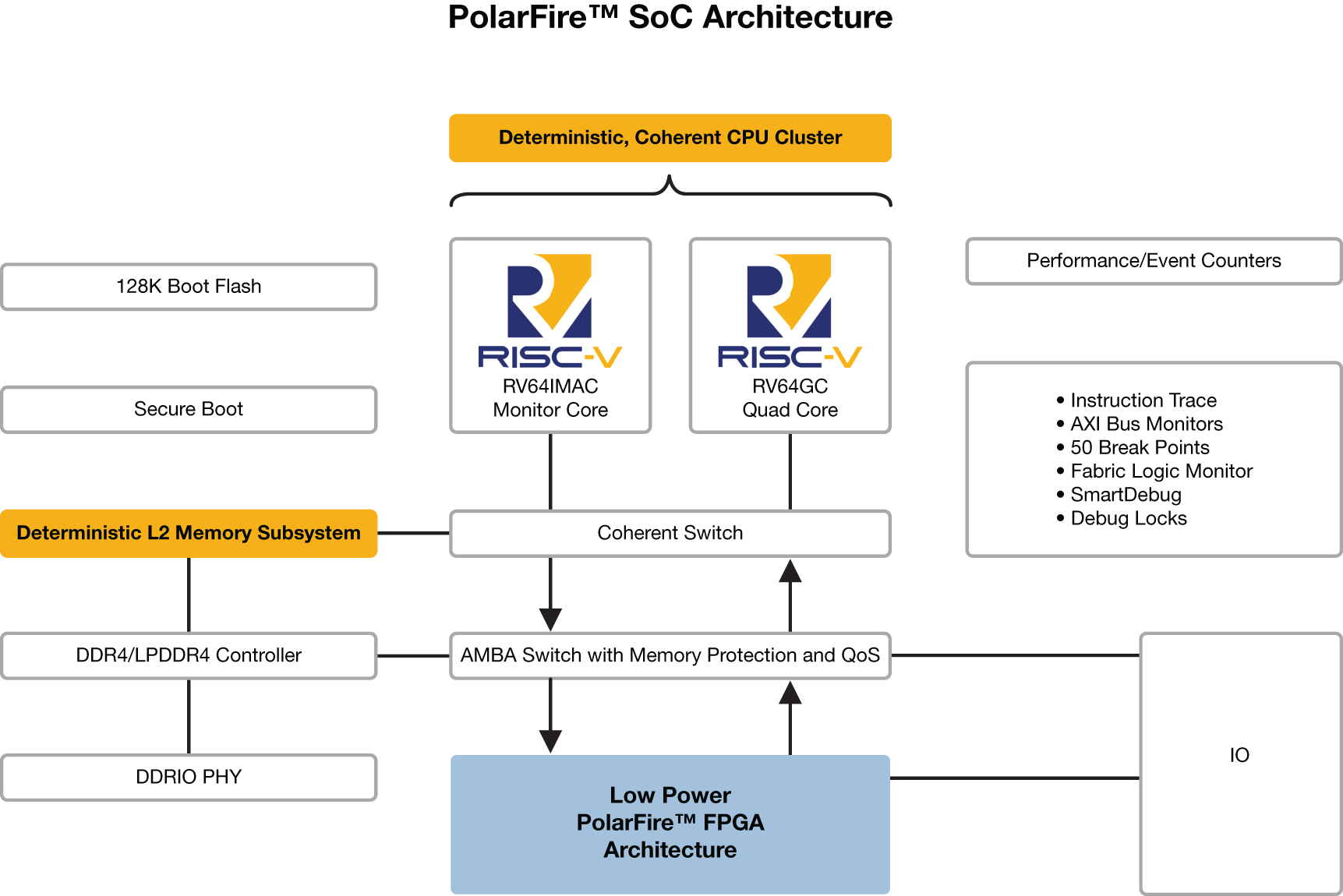

Par l’intermédiaire de sa filiale Microsemi (rachetée en mars de cette année), l’américain Microchip renforce son écosystème baptisé Mi-V lancé fin 2017 en dévoilant une architecture pour une nouvelle classe de puces-systèmes SoC qui associe les FPGA PolarFire de milieu de gamme et un sous-système processeur complet, reposant sur le jeu d'instructions ouvert et libre de droits RISC-V.... Cette architecture SoC PolarFire + RISC-V apporte aux concepteurs qui mettent au point des applications sous Linux des capacités de multitraitement asymétrique (AMP) déterministe en temps réel, fondé sur plusieurs cœurs de processeurs, précise Microchip. Développée en collaboration avec la société SiFive, spécialiste des blocs d'IP RISC-V, cette approche intègre aussi un sous-système mémoire L2 de 2 Mo, configuré en tant que mémoire cache, mémoire bloc-notes ou mémoire d’accès direct.

Les développeurs peuvent ainsi mettre en œuvre des applications embarquées déterministes temps réel, en simultané avec un système d’exploitation riche (un Linux en l'occurrence). Avec l’idée sous-jacente de pouvoir aborder un grand nombre d’applications à basse consommation dotées de contraintes thermiques et d'encombrement, dans un contexte régi par l’arrivée de la 5G, de l’apprentissage automatique et de l’Internet des objets (IoT), autant de domaines qui ont besoin de la richesse des systèmes d’exploitation bâtis sur un noyau Linux.

Ces premiers SoC FPGA à architecture RISC-V du marché apportent ainsi, selon Microchip, la prise en charge d’un Linux temps réel sur une seule puce, laissant aux développeurs de la liberté pour innover sur des systèmes faible consommation, sûrs et fiables.

Dans cette approche, les circuits SoC PolarFire intègrent des capacités de débogage complètes, incluant la trace des instructions, 50 points d'interruption, des moniteurs configurables à exécution passive de bus d’interface AXI (Advanced eXtensible Interface) et des moniteurs des matrices de FPGA, en plus de l’analyseur logique intégré à deux canaux de Microchip, SmartDebug. L’architecture intègre en outre des fonctionnalités de sécurité et de fiabilité, comme la correction SEC-DED (Single Error Correction and Double Error Detection) sur l'ensemble des mémoires, la protection de la mémoire physique, un cœur cryptographique de sécurité avec une fonction d’analyse de consommation différentielle (DPA, Differential Power Analysis), le démarrage sécurisé de qualité militaire et un processus de démarrage sur une mémoire flash de 128 Ko.

L’évaluation et la conception d'une puce-système PolarFire, qui embarque le complexe multicoeur U54-MC de SiFive, est compatible avec la plate-forme de modélisation système Antmicro Renode (issue de la société polonaise Antmicro) qui est désormais intégrée à l'environnement de développement SoftConsole de Microchip. Un kit de développement SoC PolarFire est également disponible dès à présent, composé du module d’extension HiFive Unleashed embarquant un FPGA PolarFire et de la carte de développement HiFive Unleashed de SiFive, dotée de son sous-système processeur RISC-V.

Parallèlement à cette annonce, Microchip a décidé d’étoffer l’écosystème Mi-V avec le programme Mi-V Embedded Experts, un réseau de partenariat international destiné à aider les utilisateurs à mettre en œuvre des systèmes matériels/logiciels intégrant des SoC PolarFire. Un programme qui garantit un support technique pendant tout le cycle de vie des produits développés, et qui permet d’accélérer la conception système.

-fr.jpg)