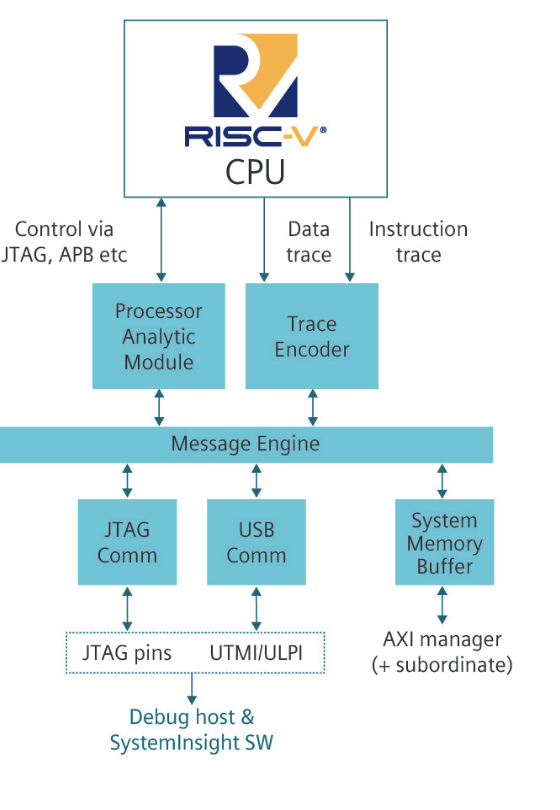

L’allemand Codasip, fournisseur de cœurs RISC-V sous forme de propriété intellectuelle et éditeur d’outils de développement pour cette architecture de processeur, propose la solution Tessent Enhanced Trace Encoder mise au point en collaboration avec Siemens EDA, et qui fait partie de la gamme de produits Tessent Embedded Analytics de cette dernière.

Grâce à cette solution commune, les développeurs peuvent tracer et déboguer les problèmes entre le silicium et les logiciels, et comprendre avec précision les comportements en temps réel, y compris, selon Codasip, sur des conceptions personnalisées complexes, fondées sur ses architectures RISC-V.

Pour rappel, les cœurs RISC-V de Codasip sont personnalisables et adaptables aux besoins d'une application. Dans ce cadre, les concepteurs système peuvent utiliser la chaîne d'outils Codasip Studio pour trouver les meilleurs compromis logiciel/matériel, mettre au point des fonctionnalités optimisées et rechercher un équilibre optimal entre consommation, performances et enpreinte silicium. Cette combinaison entre cœurs de processeur personnalisables et outils de conception assure une approche automatisée pour réaliser une puce-système maison. Pour rendre cette personnalisation accessible aux développeurs de logiciels, Codasip s'assure que tous les outils, y compris le compilateur et le débogueur, prennent en charge cette personnalisation.

Mais pour y parvenir, il faut intégrer une solution de trace. C’est l’objet du partenariat avec Siemens EDA. Car, selon Codasip, l'inclusion de l’analyse de la trace dans un SoC accélère considérablement la tâche fastidieuse de débogage logiciel et réduit les temps de mise en route et le coût de développement logiciel. Codasip a donc choisi de travailler avec Siemens EDA et son outil Trace Encoder.

Mais pour y parvenir, il faut intégrer une solution de trace. C’est l’objet du partenariat avec Siemens EDA. Car, selon Codasip, l'inclusion de l’analyse de la trace dans un SoC accélère considérablement la tâche fastidieuse de débogage logiciel et réduit les temps de mise en route et le coût de développement logiciel. Codasip a donc choisi de travailler avec Siemens EDA et son outil Trace Encoder.

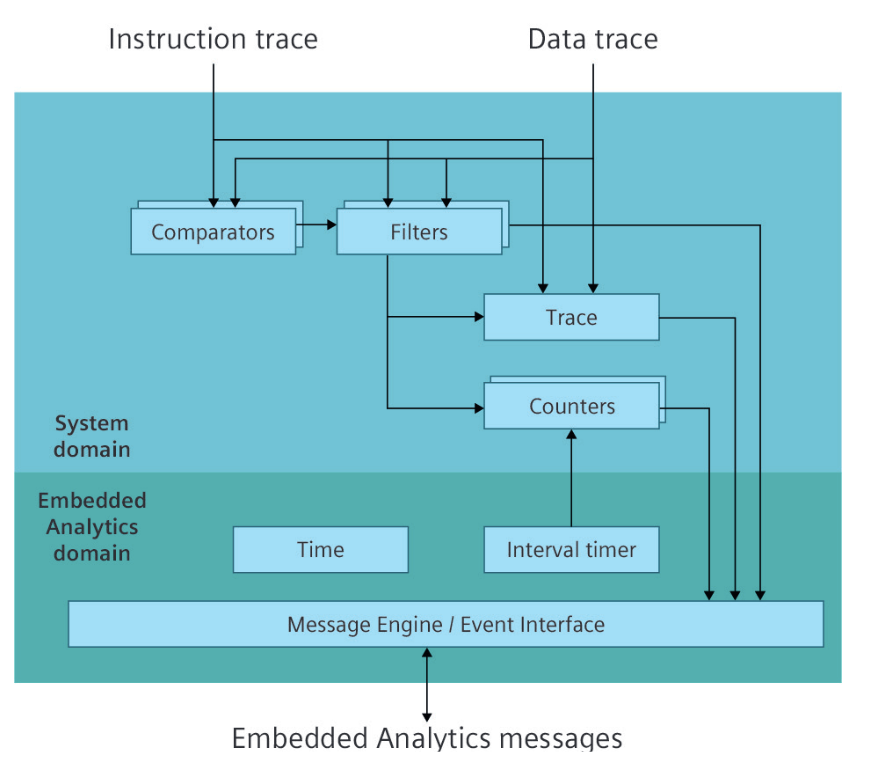

La solution complète, baptisée Tessent Enhanced Trace Encoder, s'appuie sur les spécifications RISC-V et plus spécifiquement sur les travaux du groupe de travail Debug and Trace, dirigé par des représentants de Siemens. La société a d'ailleurs mis en libre accès son algorithme de suivi de trace pour la communauté internationale RISC-V. La solution de Siemens, qui va au-delà des standards RISC-V, procure des analyses de débogage et de post-déploiement en temps réel à l'échelle du système et offre en outre aux développeurs la prise en charge d’instructions personnalisées ainsi que la mise en route d’examens détaillés au niveau système pour trouver les bogues et leur cause profonde avec une précision au niveau cycle. Ce qui signifie que le développeur obtient un aperçu de son travail de conception au niveau de chaque instruction.

« Codasip applique des normes de qualité élevées en ce qui concerne la propriété intellectuelle de ses processeurs, explique Mike Eftimakis, vice-président de la stratégie et de l'écosystème chez Codasip. Pour garantir que cela aboutisse à des systèmes finaux de haut niveau, nous souhaitions utiliser une solution de traçage allant plus loin que la spécification RISC-V. D’où le produit Tessent Enhanced Trace Encoder issu de la collaboration avec Siemens EDA, optimisé pour les systèmes complexes et personnalisés que nos clients développent. »

« Codasip applique des normes de qualité élevées en ce qui concerne la propriété intellectuelle de ses processeurs, explique Mike Eftimakis, vice-président de la stratégie et de l'écosystème chez Codasip. Pour garantir que cela aboutisse à des systèmes finaux de haut niveau, nous souhaitions utiliser une solution de traçage allant plus loin que la spécification RISC-V. D’où le produit Tessent Enhanced Trace Encoder issu de la collaboration avec Siemens EDA, optimisé pour les systèmes complexes et personnalisés que nos clients développent. »

-fr.jpg)