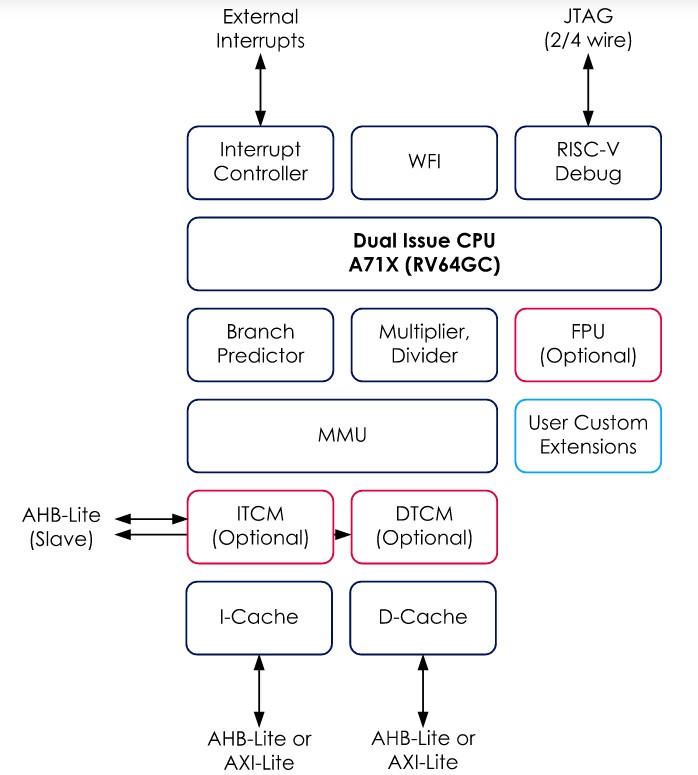

Spécialiste des cœurs de processeur embarqués RISC-V destinés aux concepteurs de puces-systèmes, la société Codasip continue d’étoffer le haut de gamme de son offre avec l’annonce du cœur A71X doté d’un double pipeline pour des performances encore améliorées. ...L’A71X est un cœur 64 bits pour processeur d’application compatible avec le jeu d’instructions RV64GC et apte à exécuter le système d’exploitation Linux.

Premier cœur superscalaire de Codasip, il peut traiter les instructions d’un même thread dans deux unités d’exécution différentes (avec la capacité donc de doubler les performances par rapport à un pipeline simple). Les diverses configurations du cœur A71X, dont la disponibilité est prévue vers la fin 2021, disposeront de toutes les caractéristiques de microarchitecture déjà annoncées fin 2020 avec le modèle A70XP, dont la prise en charge des extensions RISC-V P (pour les instructions Packet-SIMD) et la capacité à être regroupés en grappes multicœurs (jusqu’à quatre).

Premier cœur superscalaire de Codasip, il peut traiter les instructions d’un même thread dans deux unités d’exécution différentes (avec la capacité donc de doubler les performances par rapport à un pipeline simple). Les diverses configurations du cœur A71X, dont la disponibilité est prévue vers la fin 2021, disposeront de toutes les caractéristiques de microarchitecture déjà annoncées fin 2020 avec le modèle A70XP, dont la prise en charge des extensions RISC-V P (pour les instructions Packet-SIMD) et la capacité à être regroupés en grappes multicœurs (jusqu’à quatre).

Associées au double pipeline, ces caractéristiques sont jugées idéales pour la mise au point de processeurs devant traiter des flux massifs de données dans des domaines comme l’intelligence artificielle, l’apprentissage automatique, l’automobile, etc. « Il s'agit d'un ajout très important à notre portefeuille d’IP pour processeurs d'application, assure Zdeněk Přikryl, directeur technique de Codasip. Le double pipeline permettra de doper les performances sans augmentation significative de la consommation et de l’empreinte silicium, ce qui permettra de servir un spectre d'applications beaucoup plus large. »

Tous les cœurs de processeur Codasip dits d’application (ceux dont les noms de code commencent par A) sont 64 bits et utilisent une interface externe AHB ou AXI. Ils intègrent également une unité de calcul en virgule flottante et prennent en charge les instructions pour opérations de mémoire atomiques. Tous peuvent aussi exécuter Linux car ils disposent des modes de privilège machine, superviseur et utilisateur et d'une unité de gestion de la mémoire (MMU). Tous les cœurs RISC-V de Codasip, quel que soit le domaine ciblé (Low-Power Embedded, High-Power Embedded et Application), sont développés à l'aide de l’outil Codasip Studio et fournis sous forme de modèles CodAL personnalisables.

A noter que Codasip a récemment signé un accord de coopération avec la société Segger. Les sondes de débogage J-Link et l'environnement de développement intégré (IDE) Embedded Studio de Segger prennent désormais intégralement en charge les cœurs RISC-V 32 bits et 64 bits de Codasip.

-fr.jpg)