Le PICMG, consortium en charge de normes ouvertes pour l’informatique embarqué modulaire (*), vient de publier la spécification COM-HPC révision 1.3 dont l’objet est d’adapter cette norme aux besoins évolutifs de l'edge computing, de l'automatisation industrielle, des technologies médicales et des applications hautes performances.

Pour rappel, la spécification COM-HPC publiée en 2021, ouvre aux modules processeurs les applications haut de gamme en milieu industriel, exigeantes en termes de puissance de calcul et de taux de transfert de données (intelligence artificielle, réseaux 5G, fusion de données…).

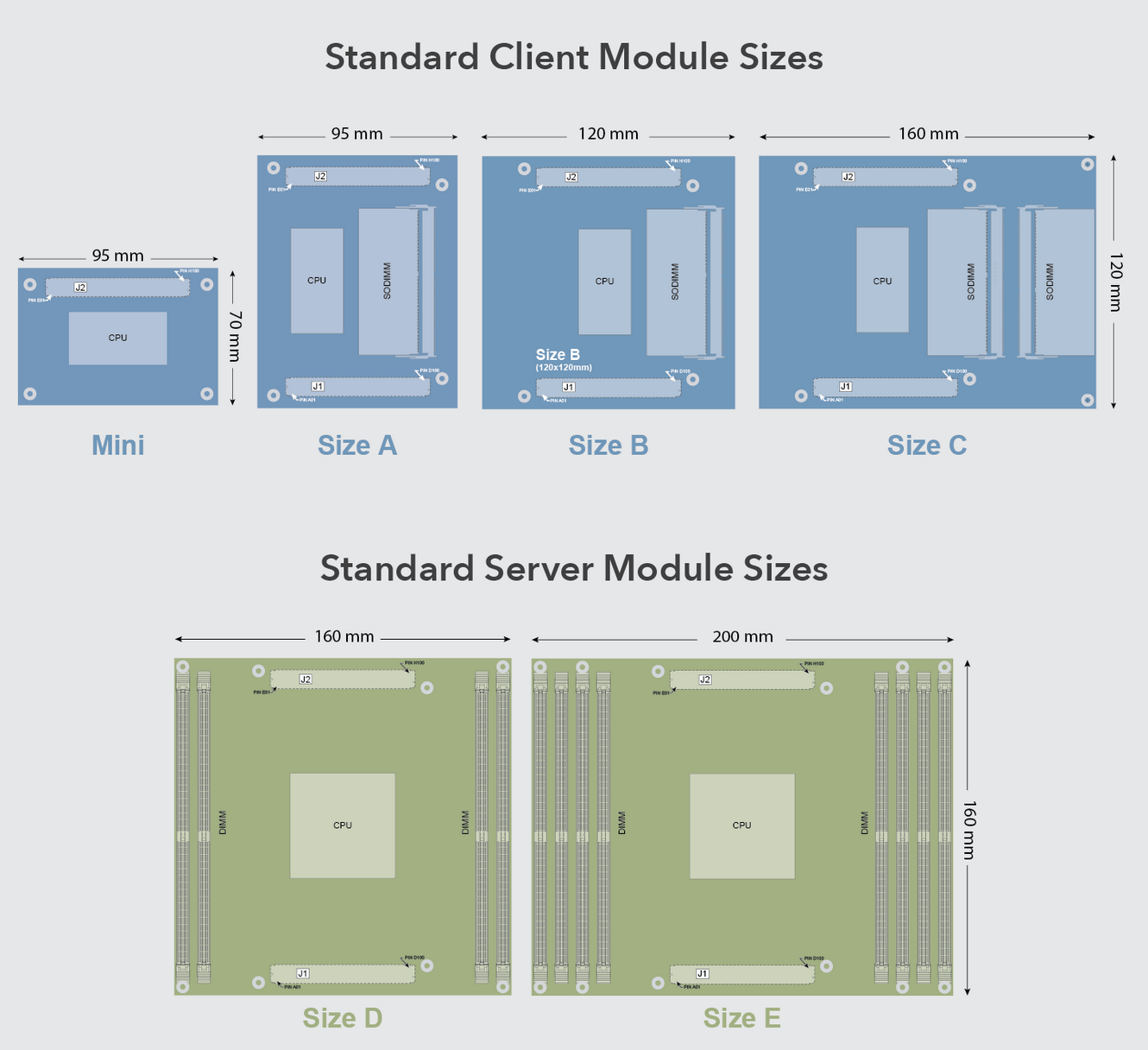

La spécification, afin de satisfaire divers besoins émergents, notamment au niveau de l’alimentation et des capacités d’extension, définit deux classes de modules COM-HPC - Client et Serveur - et cinq dimensions physiques différentes - A, B et C pour les modèles COM-HPC Client ; D et E pour les modèles COM-HPC Server - ainsi qu’une connectique commune pour les liaisons avec une carte porteuse (avec 800 broches réparties sur deux connecteurs de 400 broches).

La spécification a été complétée en 2024 par la version COM-HPC 1.2, relative aux format Mini (voir notre article) qui procure des fonctionnalités hautes performances dans un format de seulement 95 mm x 70 mm avec une seule interface à 400 broches.

Avec la version 1.3 de cette norme, présentée officiellement lors du dernier salon Embedded World, le PICMG a l’ambition de positionner le COM-HPC comme une norme d'avenir pour les architectures centrées sur l'utilisation intensive de la mémoire et sur des accélérateurs de calcul, notamment pour l'IA, favorisant ainsi de nouvelles conceptions en informatique embarquée.

Avec la version 1.3 de cette norme, présentée officiellement lors du dernier salon Embedded World, le PICMG a l’ambition de positionner le COM-HPC comme une norme d'avenir pour les architectures centrées sur l'utilisation intensive de la mémoire et sur des accélérateurs de calcul, notamment pour l'IA, favorisant ainsi de nouvelles conceptions en informatique embarquée.

Parmi les nouveautés liées à cette version, on notera la prise en charge du PCI Express Gen 6 et de l’interface CXL (Compute Express Link).

Avec le PCIe Gen 6, le COM-HPC supporte désormais des définitions supplémentaires de budget de signal pour répondre aux exigences croissantes en matière de débit de données et d’intégrité du signal.

En ce qui concerne le CXL, la spécification va autoriser une connectivité cohérente à large bande passante pour les ressources mémoire et l’accélération de calcul à travers l’interface PCIe.

De nouvelles options de connecteurs font aussi partie de la spécification COM-HPC 1.3, notamment des variantes non-BGA à colonnes, ainsi que la possibilité pour les concepteurs de faire appel à plusieurs fournisseurs de connecteurs agréés, comme Samtec, Amphenol, Hirose et All Best.

La révision ajoute en outre la prise en charge des couches physiques C-PHY sur l’interface MIPI-CSI pour les applications exigeantes à base de caméras. Au-delà, une entrée d’horloge supplémentaire prend en charge la connexion de configurations de caméra 2×2 pour la couche D-PHY.

Enfin, le PICMG indique que l’une des principales nouveautés de la norme est l’introduction du support de mode de veille moderne S0ix(**) qui permet aux modules COM-HPC de mieux prendre en charge les modes de fonctionnement à faible consommation. Les signaux de requête d’horloge PCIe bidirectionnels contribuent à ce niveau à une gestion de l’alimentation plus efficace, et les entrées d’horloge peuvent être configurées en tant que sorties d’horloge.

Ces améliorations, selon le PICMG, simplifient la conception de systèmes et optimisent le routage des signaux dans les implémentations complexes.

Au niveau des extension des entrées/sorties, la révision 1.3 affine l’utilisation des entrées/sorties à usage général (GPIO) qui peuvent désormais être affectées de manière préférentielle, par exemple, à la surveillance des états du système ou au contrôle de périphériques externes.

Cette révision définit également une interface I2S supplémentaire, améliorant notamment les capacités audio, tandis que le bus SMBus peut désormais être utilisé en option comme interface I2C supplémentaire.

(*) Les principales familles de normes développées par le PICMG, fondé en 1994, incluent le COM-HPC, le COM Express, le CompactPCI, l’AdvancedTCA, le MicroTCA, l’AdvancedMC, le CompactPCI Serial, l’InterEdge, le ModBlox7, le SHB Express, le MicroSAM et l’HPM (Hardware Platform Management)

(**) Les états S0ix représentent les différents états de veille d’une puce-système qui désactivent certaines parties du d’un circuit lorsqu'elles ne sont pas utilisées. Ces états sont déclenchés lorsque des conditions spécifiques sont remplies, permettant d’atteindre des consommation d’énergie très basse en mode sommeil profond.