Spécialiste des cœurs de processeur embarqués RISC-V personnalisables destinés aux concepteurs de puces-systèmes, la société Codasip assure avoir réalisé la première mise en œuvre commerciale de la technologie Cheri (Capability Hardware Enhanced RISC Instructions), un mécanisme de sécurité avancé développé à l'université de Cambridge et destiné à protéger les processeurs contre les cyberattaques les plus courantes.

Selon Codasip, cette technologie, qui a déjà été mise à l’épreuve sur des processeurs expérimentaux, permet de concevoir des produits sécurisés dès la conception et autorise les entreprises à prendre des mesures de sécurité préventives sans avoir à attendre les correctifs livrés par les fournisseurs desdits produits.

La société rappelle que la menace de cyberattaques augmente de jour en jour et qu’environ 70% des vulnérabilités des systèmes d'exploitation et des navigateurs documentées dans le programme Common Vulnerabilities and Exposures (CVE) au cours des deux dernières décennies sont attribuées à des erreurs mémoire logicielles. La sécurité mémoire doit donc être une préoccupation majeure pour tous les concepteurs de processeurs et de puces-systèmes SoC, les fabricants d'appareils et les utilisateurs finaux.

Or les solutions commerciales pour relever ce défi ne courent pas les rues en raison de la complexité du problème, pointe Codasip. La protection avancée de la mémoire n’est possible que par des modifications matérielles évoluées ou par des modifications logicielles coûteuses et impactantes. Mais, pour être viable dans des produits réels, affirme le fournisseur de cœurs RISC-V, toute solution proposée doit impacter de manière minimale la consommation, les performances et la surface silicium. Des exigences que Codasip estime aujourd’hui respecter avec sa nouvelle offre.

« Les produits dangereux et non sécurisés risquent de provoquer des violations de la vie privée, des atteintes à la réputation et des pertes financières inacceptables, qu'il s'agisse de véhicules, de routeurs, d'appareils médicaux ou de tout autre produit d'électronique grand public, indique Ron Black, le CEO de Codasip. L’utilisation de mécanismes de protection statistique tels que les Stack Canaries pour détecter la corruption mémoire ne s’est pas révélée suffisamment sécurisée. Il est temps que les consommateurs se posent la question de savoir si les fournisseurs de leurs appareils les protègent contre les types de cyberattaques les plus courantes. Si ces fournisseurs n’utilisent pas la technologie Cheri, ils ne le font probablement pas. »

Selon l’université de Cambridge, la technologie Cheri étend les jeux d'instructions ISA conventionnels avec de nouvelles fonctionnalités architecturales pour permettre une protection à granularité fine de la mémoire et un compartimentage logiciel à grande échelonnabilité. Les fonctionnalités de protection de mémoire de Cheri permettraient notamment d'adapter des langages de programmation historiquement dangereux pour la mémoire, tels que C et C++, afin de fournir une protection solide et efficace contre de nombreuses vulnérabilités actuellement largement exploitées.

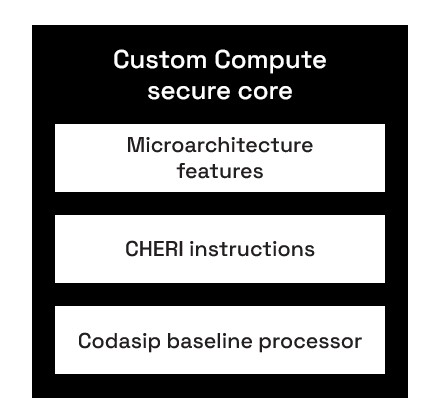

Dans le détail, Codasip, à travers l’environnement Codasip Studio, ajoute une protection mémoire intégrée à granularité fine à sa famille de processeurs 700 récemment lancée en étendant le jeu d’instructions RISC-V avec des instructions personnalisées reposant sur la technologie Cheri. Pour permettre l'utilisation de ces instructions, la société fournit également l'environnement logiciel permettant de tirer parti de cette technologie, apportant ainsi un flux de développement logiciel complet pour ajouter une protection mémoire.

Dans le détail, Codasip, à travers l’environnement Codasip Studio, ajoute une protection mémoire intégrée à granularité fine à sa famille de processeurs 700 récemment lancée en étendant le jeu d’instructions RISC-V avec des instructions personnalisées reposant sur la technologie Cheri. Pour permettre l'utilisation de ces instructions, la société fournit également l'environnement logiciel permettant de tirer parti de cette technologie, apportant ainsi un flux de développement logiciel complet pour ajouter une protection mémoire.

Les mécanismes Cheri pouvant être appliqués de manière sélective à des fonctions critiques, il est possible d'améliorer la sécurité des produits existants avec un petit effort, souvent grâce à une simple recompilation du code, affirme Codasip. L’énorme pool de logiciels C/C++ existants pourrait donc toujours être exploité dans des systèmes plus sécurisés.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à la sécurité dans les systèmes embarqués : Embedded-SEC

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV