Renesas annonce ce jour, 30 novembre 2023, avoir conçu et testé un cœur de processeur 32 bits fondé sur le jeu d'instructions ouvert RISC-V. Le fournisseur de semi-conducteurs japonais devient ainsi l'un des premiers acteurs du secteur à développer de manière indépendante un cœur CPU pour le marché des puces RISC-V 32 bits à usage général. Ce nouveau cœur de processeur RISC-V viendra renforcer le portefeuille existant de microcontrôleurs 32 bits de Renesas, notamment la famille des RX, dotés d’un cœur propriétaire, et la famille des RA, fondés sur des cœurs Arm Cortex-M.

On se rappellera que dès 2020 Renesas a commencé à s’intéresser sérieusement à l’architecture RISC-V en coopérant avec le taïwanais Andes Technology, fournisseur de cœurs de processeur embarqués RISC-V et d’un environnement de développement de puces-systèmes associé (voir notre article). En 2021, c’est avec un second spécialiste du RISC-V que Renesas s’est engagé, à savoir l’américain SiFive, par le biais d’un partenariat qualifié de stratégique par la société nippone, en vue de développer en commun des solutions RISC-V haut de gamme pour les applications automobiles (voir notre article). Ce partenariat s’accompagne de l’octroi de licences à Renesas pour l’utilisation des cœurs RISC-V de SiFive, et notamment des technologies SiFive Intelligence qui peuvent être mises en œuvre dans des puces-systèmes pour des marchés tels que le traitement audio, de la parole ou de la vision, le calcul d’inférence ou l'apprentissage automatique.

La coopération avec Andes Technology a débouché quant à elle au début de l’année 2022 par la mise sur le marché, sous le nom générique de RZ/Five, de microprocesseurs à usage générique reposant sur un cœur RISC-V 64 bits, en l’occurrence le cœur AX45MP d’Andes. Un complément aux puces RZ 32 bits et 64 bits à architecture Arm de la firme japonaise. Du fait de la puissance de ces cœurs 64 bit d’Andes, Renesas fournit ces circuits avec un paquetage Linux vérifié fondé sur la plate-forme Linux CIP (Civil Infrastructure Platform) de qualité industrielle qui dispose d’une maintenance à long terme assurée sur plus de 10 ans.

Puis dans la foulée, Renesas a annoncé fin 2022 la commercialisation du premier microcontrôleur spécifiquement optimisé pour les systèmes de commande de moteur qui repose sur le jeu d’instructions open source RISC-V, orchestré par un cœur d’entrée de gamme d’Andes Technology, associé ici à des contrôleurs A/N et N/A, des comparateurs, un capteur de température, des temporisateurs avancés pour commande moteur et des chiens de garde. Selon Renesas, les utilisateurs de ce circuit, un ASSP (Application Specific Standard Product) référencé R9A02G2020, bénéficie d'une solution clé en main prête à l'emploi pour les applications de commande moteur, avec une puce préprogrammée qui élimine les outils et les investissements logiciels liés au RISC-V.

Un "vrai" coeur RISC-V développé en interne

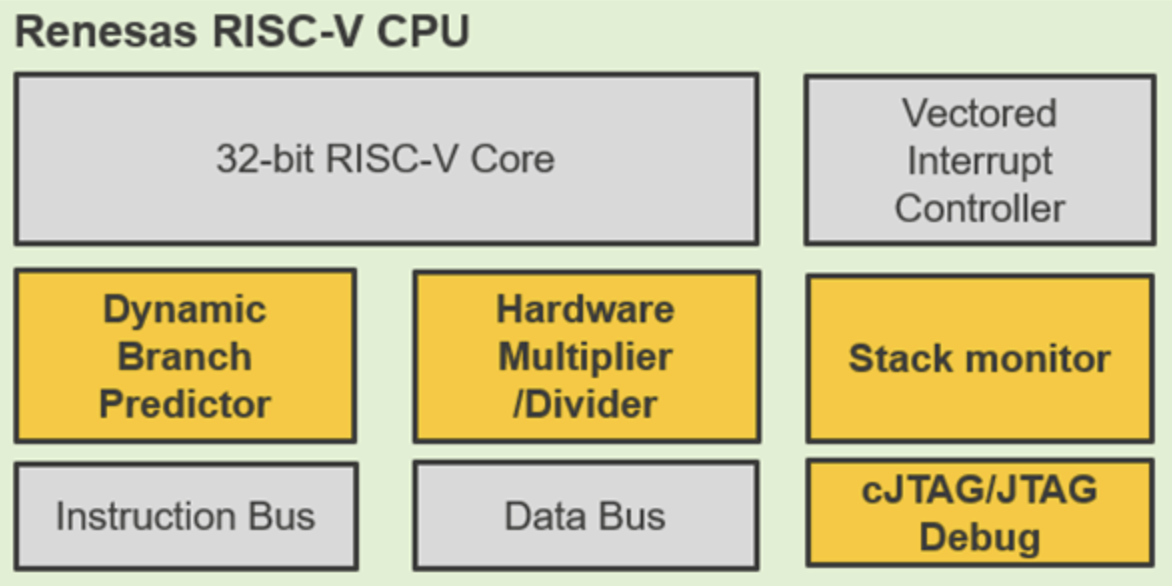

Aujourd’hui, Renesas saute donc le pas en dévoilant avoir développé et testé lui-même un cœur RISC-V 32 bits qui pourra tenir lieu, selon la société, de contrôleur d'application principal, de coeur secondaire complémentaire dans des puces-systèmes ou encore de sous-système au sein d’ASSP très intégrés (comme ceux destinés à la commande de moteurs).

« Nous nous félicitons qu’une société de la taille de Renesas, avec le poids qu’elle représente sur le marché, ait atteint cette étape dans le développement de l'architecture RISC-V 32 bits pour microcontrôleurs, commente Calista Redmond, la présidente de l’organisme RISC-V International. Cette réalisation illustre la façon dont les partenaires de l'écosystème RISC-V, tels que Renesas, font progresser l'innovation autour de la technologie RISC-V. »

Dans le détail, le cœur de processeur RISC-V de Renesas atteindrait, selon les dires de la société, une performance impressionnante de 3,27 CoreMark/MHz (*) tout en utilisant une chaîne d'outils de compilation open source fondée sur la technologie LLVM (Low Level Virtual Machine).

Dans le détail, le cœur de processeur RISC-V de Renesas atteindrait, selon les dires de la société, une performance impressionnante de 3,27 CoreMark/MHz (*) tout en utilisant une chaîne d'outils de compilation open source fondée sur la technologie LLVM (Low Level Virtual Machine).

Dans un blog écrit par Giancarlo Parodi, Principal Product Marketing Engineer, Renesas indique en outre que les développeurs pourront choisir pour ce cœur l'option RV32 “I” ou “E” en vue d’optimiser le nombre disponible de registres à usage général. Parallèlement la société indique que ce cœur sera disponible avec des extensions qui ciblent des fonctionnalités spécifiques qui vont au-delà du jeu d’instructions ISA obligatoire standard.

A ce stade, Renesas a choisi d'en intégrer quatre : l’extension M qui accélère et optimise les opérations de multiplication (et de division) en tirant parti d'un multiplicateur matériel et d'une unité de division pour une exécution d'instructions plus rapide, l’extension A qui prend en charge les instructions d'accès atomique, utiles comme fondations pour la gestion de la concurrence et des accès exclusifs, généralement dans des systèmes utilisant des systèmes d’exploitation temps réel, l’extension C qui définit des instructions compressées codées en 16 bits, ce qui permet d’économiser de l'espace mémoire pour les instructions courantes et de sélectionner ces optimisations par le compilateur, et enfin l’extension B qui ajoute plusieurs instructions pour la manipulation des bits, un avantage dans les applications gérant des registres périphériques, des protocoles et des structures de données fondées sur des valeurs codées par champ de bits.

Ces extensions permettent au concepteur de choisir les éléments à inclure dans le processeur, en fonction de son cas d'utilisation cible, et par conséquent d'optimiser le compromis entre consommation d'énergie, performances et empreinte silicium.

Signalons enfin pour être complet que Renesas échantillonne d’ores et déjà des circuits architecturés autour de ce nouveau cœur et prévoit de lancer son premier microcontrôleur à cœur RISC-V maison, ainsi que les outils de développement associés, au premier trimestre 2024 (des annonces seront probablement faites à l’occasion du salon Embedded World qui se tiendra à Nuremberg en avril 2024).

(*) De plus amples détails sur ce score seront disponibles sur le site de l'EEMBC (Embedded Microprocessor Benchmark Consortium) une fois le premier produit dévoilé début 2024.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV