Les sociétés Lauterbach et UltraSoC, toutes deux spécialisées dans les technologies de débogage de puces-systèmes SoC, travaillent de concert pour apporter aux utilisateurs des architectures open source RISC-V un environnement de débogage et d’analyse de trace indépendant des concepteurs de circuits. ... Cette collaboration, dont les premiers fruits ont été montrés lors du salon Embedded World qui s’est tenu fin février dernier, consiste à étendre les fonctionnalités des outils des deux sociétés vers le RISC-V, et à les combiner entre elles.

Le britannique UltraSoC propose, de son côté, une solu tion d’analyse de la trace des processeurs RISC-V tandis que, de l’autre, l’allemand Lauterbach adapte son outil de débogage Trace32 aux exigences de cette architecture de processeur open source. En combinant les deux technologies, les développeurs pourront avoir accès à de puissants outils d'analyse de débogage, de traçage et d'analyse logique avec en ligne de mire une réduction significative des temps de développement sur le RISC-V.

tion d’analyse de la trace des processeurs RISC-V tandis que, de l’autre, l’allemand Lauterbach adapte son outil de débogage Trace32 aux exigences de cette architecture de processeur open source. En combinant les deux technologies, les développeurs pourront avoir accès à de puissants outils d'analyse de débogage, de traçage et d'analyse logique avec en ligne de mire une réduction significative des temps de développement sur le RISC-V.

Une approche qui permet donc de choisir à la fois le bloc d’IP de débogage mis en œuvre dans une puce RISC-V (en provenance d’UltraSoC) et l'environnement dans lequel les concepteurs développent et déboguent (en provenance de Lauterbach). Et ce sans être corseté par des outils de développement liés à un fournisseur de circuits particulier.

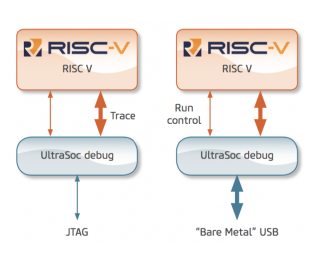

Pour ce faire, UltraSoC intègre de manière non intrusive un bloc d’IP d’instrumentation et de débogage au sein du SoC, tandis que les données récoltées par cette IP sont ensuite envoyées via une interface JTAG dans l’environnement Trace32 pour y être exploitées.