Proposée aux développeurs par le britannique Imperas, la version 1.0 de l'interface de vérification RISC-V standard et ouverte RVVI (RISC-V Verification Interface) procure, dixit la société, l'adaptabilité et la réutilisation de son IP de vérification à la communauté des développeurs qui effectuent la vérification de processeurs à architecture RISC-V.

L'interface RVVI est présentée par Imperas comme le socle de l’écosystème de vérification du RISC-V qui, du fait de son succès, fait migrer la responsabilité de la vérification, jusqu'ici limitée à quelques fournisseurs d’IP, vers tous les développeurs qui choisissent d'exploiter les libertés de conception du RISC-V.

Ces dernières années, note le Britannique, les écosystèmes clés pour une adoption réussie des processeurs RISC-V se concentraient sur les logiciels (outils de développement, compilateurs et systèmes d'exploitation) et le matériel (outils de CAO pour la simulation RTL, synthèse au niveau des portes logiques et génération du layout physique). Dans ce paysage, la tâche de vérification était effectuée en interne par les fournisseurs d’IP RISC-V avec des techniques propriétaires, si bien que les cœurs de processeur n’ont été que très rarement testés par les équipes qui ont adopté une puce-système à architecture RISC-V. Désormais, à leur tour, tous les développeurs qui choisissent d'étendre, de modifier ou de construire un cœur de processeur personnalisé vont pouvoir répondre aux exigences de vérification de la conception.

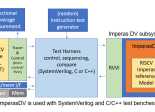

Dans ce cadre, Imperas a récemment annoncé la solution ImperasDV avec une combinaison d'un modèle de référence, de suites de tests et d'une méthodologie de vérification pour répondre à l'ensemble du spectre des implémentations RISC-V., le fichier RTL du composant sous test étant généralement configuré avec un banc d'essai pour contrôler et surveiller l'analyse opérationnelle pendant le processus de vérification. Et ce avec la prise en charge par le banc de test de toutes les fonctionnalités du noyau, y compris les tâches de vérification spécifiques pour le test et l'analyse à travers des opérations de débogage. Comme le banc de test s'interface avec le processeur au niveau RTL, les générateurs de tests, le modèle de référence, l'IP de vérification et les outils de CAO pour la simulation RTL, toute erreur ou omission a un impact significatif sur la qualité du test avec la possibilité de laisser passer des erreurs lors des dernières étapes de la conception. A ce niveau, souligne Imperas, bien qu'un banc de test personnalisé puisse être créé pour n'importe quel processeur cible sous test, cette approche limite les options de réutilisation.

Le nouveau standard et méthodologie RVVI qui, selon Imperas, évite cet écueil est fondé sur une spécification ouverte (voir sur GitHub) et peut désormais être adapté à toute configuration autorisée dans les spécifications RISC-V. En adoptant la norme RVVI, les développeurs peuvent ainsi tirer parti de tous les composants courants prêts à l'emploi et explorer des options supplémentaires avec une IP de vérification tierce.

De plus, étant donné que de nombreux projets évoluent vers de nouvelles améliorations pour les conceptions ultérieures, l'investissement dans l'infrastructure de vérification peut être réutilisé; à la fois pour les futurs projets principaux et les test de régression en cours.

En résumé, le standard ouvert RVVI fournit une intégration transparente entre RTL, modèle de référence et banc de test logiciel, ainsi qu'une intégration à couplage direct, la prise en charge des pipelines du processeur, la conformité à la norme UVM (méthodologie de vérification universelle pour vérifier les conceptions de circuits intégrés) et le support du langage SystemVerilog compatible avec les outils de conception proposés par Cadence, Siemens EDA, Synopsys…

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)