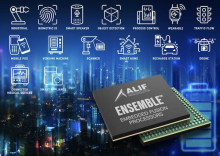

[APPLICATION ALIF SEMICONDUCTOR] Couplage étroit d’un NPU avec un CPU, intégration de l’ensemble du système, gestion adaptative de l’alimentation et protection des IP intégrées font l’objet d’une forte demande de la part des fabricants de terminaux alimentés sur batterie. A ce niveau, les concepteurs qui évaluent la famille des circuits Ensemble d’Alif Semiconductor trouveront des solutions allant d’un seul cœur de CPU à des systèmes à quatre cœurs supportant le système d’exploitation Linux en vue de s’adapter à des projets variés tout en permettant la réutilisation de logiciels existants. Une analyse en détail d’Alif Semiconductor.

Auteur : Mark Rootz

Auteur : Mark Rootz

Vice-président du marketing

Alif Semiconductor

L’intégration de l’intelligence artificielle (IA) dans les appareils terminaux peut transformer radicalement leur valeur. Par exemple, dans le domaine médical, les appareils portables dotés d’algorithmes d’IA promettent une détection et un diagnostic des affections graves telles que la fibrillation auriculaire hors de la clinique pour l’intégrer dans le quotidien du patient et en assurer le suivi.

Autre exemple, à l’aide d’algorithmes d’IA, les aides auditives peuvent être transformées d’un simple amplificateur en un discriminateur vocal intelligent, isolant la voix de la personne visée, tout en annulant tous les autres bruits et voix, ou en les mettant en sourdine dans l’arrière-plan sonore. Ces capacités liées à l’exploitation de l’IA pourraient multiplier la valeur de presque tous les types de produits portables ou sur batterie.

Cependant, au niveau du terminal, la plupart du temps on sait que les fonctions d’IA ne peuvent pas être exécutées dans le cloud pour des questions de puissance, de latence, de respect de la vie privée, de portée sans fil, de sécurité et de coût. Ces appareils ont donc besoin d’une capacité locale de traitement pour gérer de manière autonome leurs applications d’IA.

Mais, pour réussir le déploiement local de l’IA dans ces produits, il faut trouver un moyen de dépasser les importantes contraintes d’espace et d’énergie qui pèsent sur les concepteurs. Les appareils portables tels que les écouteurs, les bagues, les lunettes connectées et les moniteurs de patients, par exemple, disposent de petits boîtiers qui ne peuvent contenir que peu de composants et une petite batterie. Avant la déferlante de l’IA, bon nombre de ces produits étaient fondés ur des microcontrôleurs ou des microprocesseurs à usage général qui pouvaient gérer les fonctions principales attendues, facilitant le travail des ingénieure à atteindre leurs objectifs en matière d’espace et de puissance tout en réduisant le nombre de composants et l’encombrement de la carte.

À l’ère de l’IA, cette intégration des fonctions du système dans un microcontrôleur à usage général reste une voie classique pour économiser de l’espace et de l’énergie. Toutefois, un tel circuit doté de fonctions d’IA doit désormais intégrer encore plus de fonctions, tout en affichant une consommation d’énergie ultra-faible. Il s’agit ici que les appareils dotés de petites batteries soient capables de gérer des calculs d’IA sans sacrifier la durée d’utilisation entre les charges. La quadrature du cercle. Face à cette situation, il ne s’agit donc pas simplement d’intégrer une capacité d’IA sur une architecture de microcontrôleur ancienne mais de créer une nouvelle génération de ce type d’architectures compatibles avec l’IA pour les appareils portables alimentés par des batteries.

C'est ce qu’a réaliser Alif Semiconductor, fondée en 2019, qui a eu l’avantage de réfléchir dès le départ sur la façon d’intégrer l’IA directement au sein de ce type de circuit. Les développements réalisés reflètent des centaines de conversations au cours desquelles les équipementiers ont décrit à Alif les facteurs qui influencent leur choix de microcontrôleur pour servir de puce-système (SoC, System On Chip) pour les appareils terminaux alimentés sur batterie. De ses discussions, quatre principaux facteurs ont été mis en avant.

L’accélération du traitement neuronal doit être étroitement couplée au processeur

La réponse initiale du marché a consisté à mettre au point des kits de développement logiciel (SDK, Software Develoment Kit) pour permettre aux algorithmes d’IA et d’apprentissage automatique (ML, Machine learning) de fonctionner sur le même coeur Arm Cortex-M que celui qui exécute les fonctions de contrôle conventionnelles.

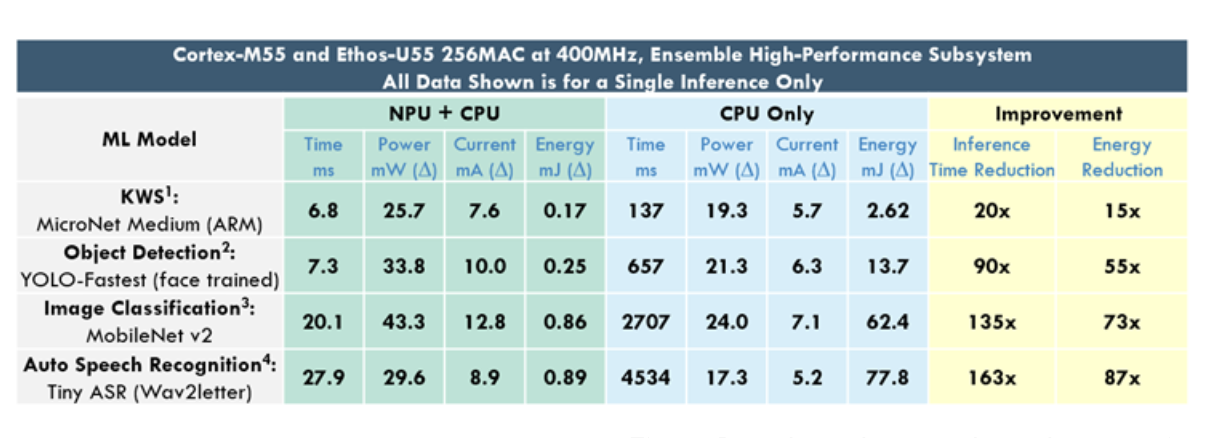

Cependant, un microcontrôleur destiné aux applications ML de terminal a besoin d’une unité de traitement neuronal (NPU, Neural Processeur Unit), cette dernière étant optimisée pour les opérations de multiplication et d’accumulation qui sont le cœur des applications de réseaux neuronaux. Un CPU embarqué seul aura du mal à gérer ces charges de travail ML significatives, car les inférences dérivées du réseau ML hautement parallèle doivent être résolues en série, ce qui prend du temps et consomme beaucoup d’énergie. On voit sur la tableau ci-dessous le contraste des performances d’une IA entre un CPU et un NPU intégré au sein d’un microcontrôleur.

A ce niveau, la gamme des circuits Ensemble d’Alif Semiconductor utilise le cœur de CPU Arm Cortex-M55 associé à un coprocesseur NPU Arm Ethos-U55. Les métriques montrent une seule inférence ML pour quatre modèles ML entraînés exécutés sur un MCU Ensemble, et les modèles représentent les opérations requises pour la reconnaissance de mots clés, la détection d’objets, la classification d’images et la reconnaissance vocale.

On voit notamment que le coeurs Cortex-M55 utilisé dans les circuits d’Alif affiche des résultats qui sont déjà de l’ordre de 5 fois supérieurs pour les charges de travail ML par rapport aux générations précédentes de CPU à base de coeurs Cortex-M.

Cependant, aussi bon que soit le Cortex-M55, les chiffres des colonnes jaunes révèlent une augmentation substantielle des performances de près de deux ordres de grandeur d’amélioration en utilisant l’association NPU+CPU par rapport au CPU seul. Considérant que le Cortex-M55 est déjà cinq fois plus performant que précédemment, on peut raisonnablement multiplier à nouveau ces gains par cinq. Pour la reconnaissance vocale, cette architecture est environ 800 fois plus rapide et 400 fois moins énergivore par inférence comparé aux CPU à coeurs Cortex-M anciens.

Les tests comparatifs montrent une performance et une efficacité supérieures d’un NPU par rapport à un CPU lors de l’exécution de fonctions ML courantes

L’environnement de développement logiciel est un autre facteur important pour le couplage étroit du NPU au CPU. Il existe à ce niveau de nombreuses options pour déployer des cœurs NPU tiers brevetés au sein de SoC. Les équipementiers sont cependant très clairs : ils ne veulent pas réorganiser toute leur infrastructure de développement pour travailler avec une nouvelle architecture uniquement pour les charges de travail IA/ML, ce qui nécessiterait l’adoption de nouvelles chaînes d’outils et de nouveaux jeux d’instructions.

S’ils travaillent déjà dans l’écosystème Arm pour les fonctions de contrôle embarquées, ils veulent également rester dans l’écosystème Arm pour les fonctions IA/ML. La combinaison d’un CPU Cortex-M et d’un NPU Ethos-U d’Arm répond à cette exigence.

En fait, le NPU Ethos-U est essentiellement un coprocesseur qui s’intègre de manière transparente au CPU à coeurs Cortex-M. Le compilateur Arm Vela distribue automatiquement la charge de travail ML entre les deux, 95 % ou plus revenant généralement au NPU. L’autre avantage est que le CPU à coeurs Cortex-M peut être en veille ou effectuer d’autres tâches pendant que l’inférence ML est activée.

L’intégration doit englober l’ensemble du système

Il est juste de dire que le NPU est susceptible d’être au centre de l’attention dans un microcontrôleur en charge de l’exécution de d’applications d’IA et de ML. Cependant, les éléments intégrés autour des cœurs de traitement, et en particulier la manière dont l’intégration est conçue, sont très importants. En tête de liste figurent la mémoire et les périphériques.

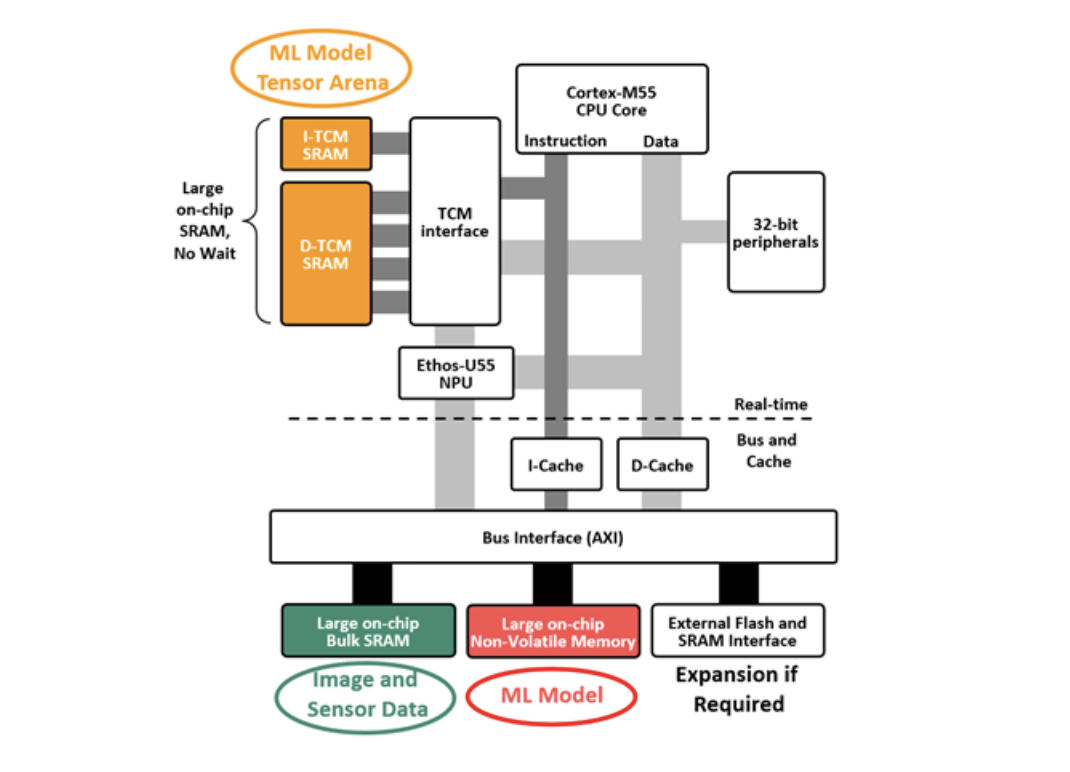

On voit sur le tableau mentionné plus haut qu’une capacité de traitement améliorée est essentielle pour des performances élevées et une grande efficacité énergétique, mais que sans un système de mémoire optimisé, les résultats ne seront pas à la hauteur des attentes.

Sur la figure ci-dessous qui présente une vue simplifiée de la topologie de la mémoire d’un micrcontrôleur Ensemble, la moitié supérieure représente la section en temps réel, avec une mémoire à faible latence très rapide connectée aux cœurs CPU et NPU. Pour des inférences rapides, ces mémoires Sram doivent être suffisamment grandes pour contenir la zone de tenseurs du modèle ML.

La moitié inférieure du schéma présente d’autres mémoires du système reliées par un bus commun à grande vitesse. Une mémoire Sam de grande capacité et partagée est ici nécessaire pour contenir les données des capteurs, telles que les entrées d’une caméra et des microphones, et une grande mémoire non volatile contient le modèle l’algorithme d’apprentissage automatique lui même ainsi que le code d’application. Lorsque de grandes mémoires sur puce sont distribuées de cette manière pour minimiser le trafic concurrent sur le bus, les transactions de mémoire concurrentes prospèrent, les goulets d'étranglement sont éliminés, les temps d’accès à la mémoire sont réduits et la consommation d’énergie est compatible avec l’utilisation d’une petite batterie.

Topologie de mémoire interne des MCU Ensemble

Un bon ensemble de périphériques est également essentiel pour les microcontrôleurs dans les applications ML de terminal qui fonctionnent souvent dans un ou plusieurs des domaines vision, voix et vibration.

Cette approche signifie qu’une connectivité avec des capteurs d’images, des microphones, des unités de mesure inertielle et autres est nécessaire, en plus des périphériques traditionnels, tels que les canaux série à grande vitesse, les interfaces analogiques et les interconnexions d’affichage. Pour les appareils terminaux dopés l’IA, toutes ces fonctions doivent être intégrées dans le microcontrôleur.

L’intégration de l’ensemble du système élimine à ce niveau non seulement le besoin de rails d’alimentation supplémentaires et de conversion d’énergie, comme un circuit intégré de gestion d’énergie (PMIC, power management integrated circuit) externe, mais permet également de contrôler dynamiquement l’alimentation à un niveau beaucoup plus granulaire sur la puce

Gestion adaptative de l’énergie pour prolonger l’autonomie de la batterie

Alif a su voir que la concentration des capacités ML locales sur un système final allait s’envoler dans un avenir proche, tandis que la taille physique de ces produits diminuerait rapidement, notamment ceux utilisant des batteries de plus en plus petites.

L’approche d’Alif pour augmenter l’autonomie de la batterie afin de répondre à ce problème a pris plusieurs formes dont voici deux exemples notables.

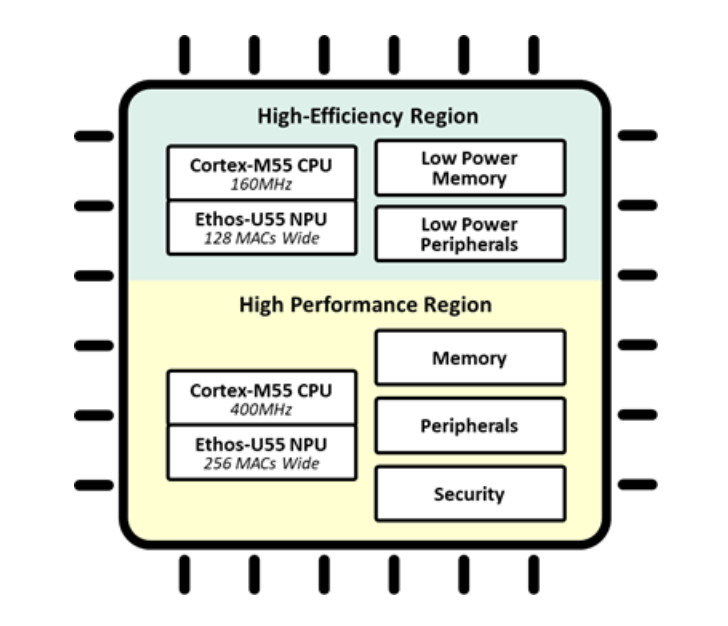

- Le partitionnement du système est conçu de manière à ce qu’une partie de la puce à faible consommation d’énergie soit toujours active, mais offre toujours une solide capacité de calcul qui lui permet de réveiller sélectivement une partie bien plus performante de la puce pour exécuter des charges de travail lourdes, puis de se remettre en veille.

- Le système de gestion d’énergie n’allume dynamiquement que les parties de la puce nécessaires et les éteint lorsqu’elles ne sont pas requises, le tout à un niveau granulaire fin.

Pour faciliter cette répartition des fonctions, de nombreux microcontrôleurs Ensemble possèdent deux paires de cœurs Cortex-M55+Ethos-U55, comme le voit sur la figure ci-dessous. L’une d’elles se situe dans la région à haut rendement de la puce, construite sur des transistors à faible courant de fuite qui peuvent être toujours actifs et fonctionner jusqu’à 160 MHz. L’autre paire se trouve dans la région haute performance fonctionnant jusqu’à 400 MHz.

Pour comprendre leur intérêt, imaginons une caméra de détection de présence connectée qui balaie une pièce en continu à une faible fréquence d’images en utilisant la paire de cœurs à haut rendement pour classer un événement valide (comme la chute d’un être humain ou un geste spécifique). Ce qui réveille alors la paire haute performance pour identifier une ou des personnes, vérifier si des sorties sont bloquées, appeler à l’aide, etc.. Dans ce cas, la caméra réalise un contrôle intelligent, moins de faux positifs et prolonge l’autonomie de la batterie.

Des utilisations similaires de ces deux paires de cœurs CPU+NPU peuvent être appliquées de manière tout aussi pertinente à la classification des sons, des voix, des mots, des textes, des vibrations et des données de capteurs dans des applications variées.

Synoptique du MCU Ensemble E3 montrant les régions à haut rendement et haute performance de la puce.

En outre, tous les micrcontrôleurs Ensemble utilisent la technologie aiPM (gestion intelligente et autonome de l’alimentation) d’Alif pour manipuler en temps réel jusqu’à 12 domaines d’alimentation individuels dans la puce en fonction de l’utilisation en cours. Seuls les domaines qui exécutent activement des tâches sont mis sous tension (comme ceux qui alimentent des cœurs de traitement spécifiques, des mémoires ou des périphériques), tandis que les autres domaines restent éteints.

Protection des modèles d’apprentissage machine et de la propriété intellectuelle

La dernière fonctionnalité clé qui doit être intégrée dans un microcontrôleur avec une IA intégrée destiné aux terminaux est l’IP (bloc de propriété intellectuelle) . Il s’agit d’abord de résister aux formes omniprésentes de cyber-attaques, mais pour de nombreux équipementiers, la protection la plus importante concerne l’IP intégrée dans les modèles d’IA.

Ces derniers investissent beaucoup de temps et d’argent dans la collecte d’ensembles de données d’entraînement, dans la construction de modèles d’IA et dans le développement et le perfectionnement d’algorithmes d’inférence. Les fabricants peu scrupuleux sont donc fortement incités à voler cette IP coûteuse en la copiant à partir d’unités de production insuffisamment protégées.

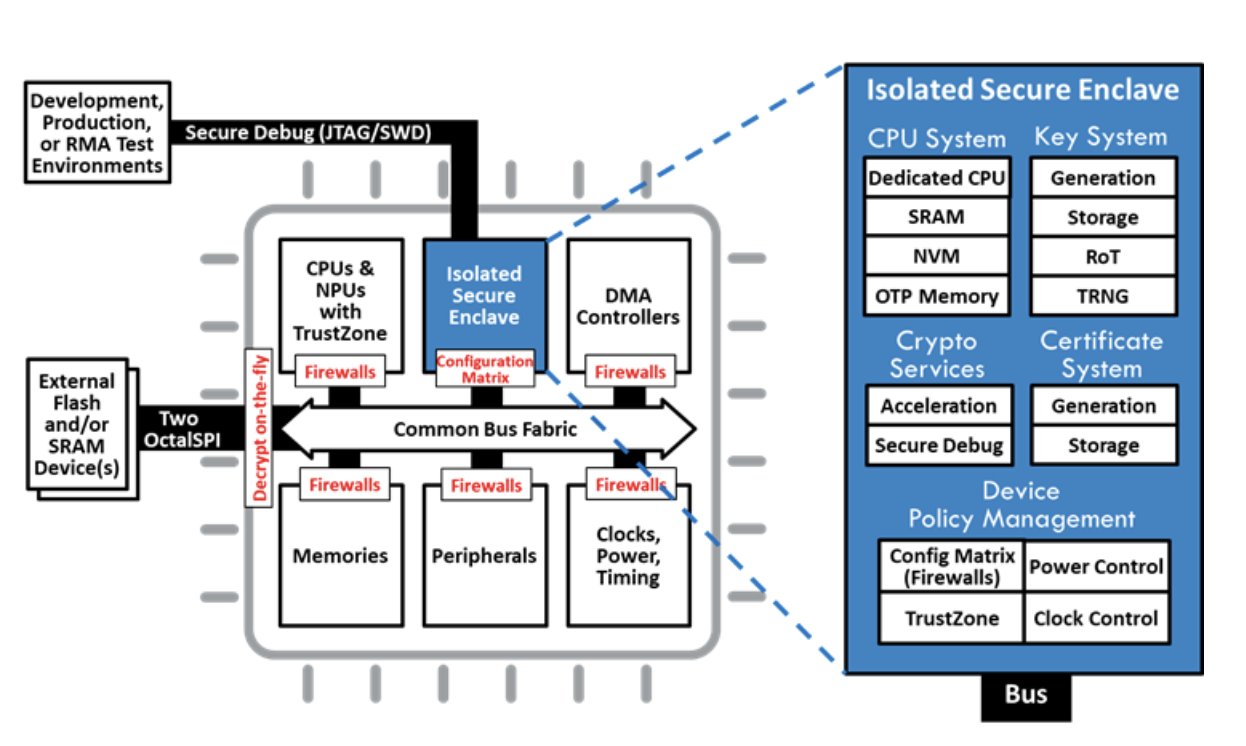

Un microcontrôleur externe sécurisé permet à l’équipementier d’établir une racine de confiance, de gérer les clés secrètes et les certificats, de faciliter un démarrage sécurisé, etc. L’utilisation d’un MCU sécurisé externe est donc une approche courante pour intégrer une sécurité forte dans les conceptions basées sur un MCU conventionnel, mais il est rare de trouver une "enclave" sécurisée complète avec ces fonctions, et plus encore, intégrées dans un MCU conventionnel.

Pourtant, les produits IA portables sur batterie profitent particulièrement des économies d’espace et d’énergie, ainsi que d’une sécurité accrue lorsque cette fonctionnalité est intégrée dans directement dans le microcontrôleur.

L’enclave sécurisée que l’on voit sur la figure ci-dessous, installée en série sur tous les circuits d’Alif, est un sous-système isolé centré sur la gestion des fonctions de sécurité essentielles telles que la gestion et le stockage des clés sécurisées, le démarrage sécurisé avec une racine de confiance immuable, une attestation lors de l’exécution utilisant des certificats, des services de cryptographie matérielle, un débogage sécurisé, une protection de lecture, des mises à jour de firmware sécurisées, une gestion complète du cycle de vie.

L’enclave sécurisée des MCU Ensemble régit la politique de sécurité pour l’ensemble de la puce

Note de bas de page pour le tableau

1) KWS : Extrait du document ARM MicroNets. Int8 quantifié, entraîné sur l’ensemble de données « Google Speech Commands ». Empreinte du modèle : 154 Ko MRAM, 28 Ko SRAM

2) Détection d’objet : Résolution 192x192 en niveaux de gris et en couleur. Int8 quantifié, entraîné sur l’ensemble de données « WIDER FACE ». Empreinte du modèle : 431 Ko MRAM, 433 Ko SRAM

3) Classification des images : Résolution 224x224, 24 bits, couleur. Int8 quantifié, entraîné sur l’ensemble de données « ImageNet ». Empreinte du modèle : 3,552 Ko MRAM ; 1,47 Ko SRAM

4) ASR : Wav2letter réduit et optimisé, intégré dans l’application de démonstration ML d’ARM, exécutant un cas d’utilisation ASR. MRAM=2 346,06 Ko (largement optimisé par Vela à partir de 3 903,43 Ko), SRAM=1 197,20 Ko

-fr.jpg)