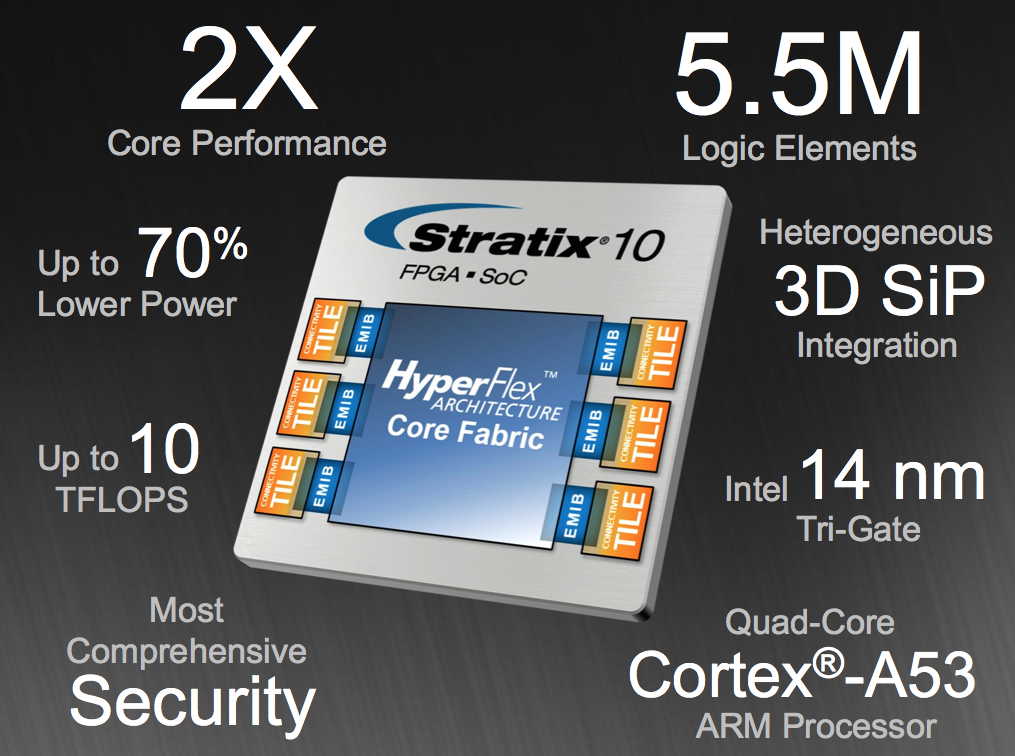

Le fournisseur de circuits programmables Altera vient de dévoiler les caractéristiques architecturales et les détails de ses FPGA et SoC Stratix 10 haut de gamme basés sur le procédé de fabrication 14 nm Tri-Gate d’Intel. A la clé, ...5,5 millions d'éléments logiques dans une puce monolithique, un boîtier de type SiP (System In Package) 3D hétérogène qui combine la matrice FPGA avec des transceivers à haute vitesse (jusqu’à 144 pour une bande passante série 4 fois supérieure à celle de la génération précédente, soit 56 Gbit/s pour les plus rapides) et des blocs DSP à virgule flottante capables de réaliser des opérations en virgule flottante à un débit atteignant 10 Tflops. Les SoC FPGA intègrent en outre un processeur 64 bits ARM Cortex-A53 à quatre cœurs, fonctionnant jusqu'à 1,5 GHz. Marchés visés : avant tout les centres de données, les systèmes de radar et les systèmes de calcul à haute performance.

Pour parvenir à ces performances inédites, Altera s’appuie en particulier sur une architecture interne novatrice pour ses circuits, baptisée HyperFlex, qui permet, selon la société, de doubler les performances internes des cœurs logiques du FPGA par rapport aux générations précédentes. Concrètement, l'architecture HyperFlex incorpore des registres sur tous les segments de routage d’interconnexions de la matrice du FPGA, permettant aux circuits Stratix 10 de supporter des technologies d’optimisation de conception comme la réévaluation de timing (register retiming) ou la mise en place de pipelines de données via les registres (register pipelining), difficiles à mettre en place sur les architectures conventionnelles de FPGA. L'architecture HyperFlex permet in fine aux concepteurs de minimiser les retards de propagation des signaux induits par les chemins critiques du routage et d'atteindre rapidement les objectifs en termes de timing. Cette approche permet en outre, selon Altera, de réduite de manière drastique la consommation, jusqu’à 70%, en réduisant la taille de la logique.

Parallèlement, l’intégration du circuit dans un SiP 3D hétérogène qui fait appel à la technologie propriétaire EMIB (Embedded Multi-die Interconnect Bridge) d’Intel permet de “loger” une matrice FPGA monolithique à haute densité (jusqu'à plus de 5,5 millions d'éléments logiques) avec d'autres composants. Notamment les émetteurs-récepteurs et leurs protocoles associés qui se présentent sur ces circuits sous la forme de “tuiles” connectées à l’extérieur de la logique, et qui sont facilement interchangeables en production. Offrant la possibilité à Altera de fournir rapidement différentes versions des composants Stratix 10 répondant aux évolutions des marchés. La technologie permet ainsi de supporter des transceivers rapides (jusqu’à 56 Gbit/s), des formats de modulation émergents (comme le PAM-4) ou des standards de communication de dernière génération comme le PCIe Gen4 ou le Multi-Port Ethernet.

Parallèlement, l’intégration du circuit dans un SiP 3D hétérogène qui fait appel à la technologie propriétaire EMIB (Embedded Multi-die Interconnect Bridge) d’Intel permet de “loger” une matrice FPGA monolithique à haute densité (jusqu'à plus de 5,5 millions d'éléments logiques) avec d'autres composants. Notamment les émetteurs-récepteurs et leurs protocoles associés qui se présentent sur ces circuits sous la forme de “tuiles” connectées à l’extérieur de la logique, et qui sont facilement interchangeables en production. Offrant la possibilité à Altera de fournir rapidement différentes versions des composants Stratix 10 répondant aux évolutions des marchés. La technologie permet ainsi de supporter des transceivers rapides (jusqu’à 56 Gbit/s), des formats de modulation émergents (comme le PAM-4) ou des standards de communication de dernière génération comme le PCIe Gen4 ou le Multi-Port Ethernet.

Les Stratix 10 sont disponibles, dans leur configuration SoC, avec un processeur intégré (HPS, Hard Processor System) ARM 64 bits à quatre cœurs Cortex-A53 doté en particulier d’une unité de gestion de la mémoire système, de contrôleurs de mémoire externe et d’interfaces de communication à haute vitesse.

Enfin, côté sécurité, les Stratix 10 intègrent un Secure Design Manager (SDM) innovant qui assure l'authentification et le cryptage, l'authentification multifacteur et la technologie dite PUF (Physically Unclonable Function). Pour cette partie, Altera a conclu un partenariat avec les sociétés Athena Group et IntrinsicID portant sur un accélérateur de cryptage et un bloc d’IP PUF.

-fr.jpg)