Alors que les possibilités offertes par les circuits programmables de type FPGA ou SoC (associant matrice de FPGA et cœurs de processeur) vont croissantes, la productivité des outils de développement peinent à suivre le mouvement ...imposé par les innovations au niveau matériel. Comme tous les fournisseurs de circuits programmables, Altera doit faire face à cette situation, et a décidé en conséquence de lancer un nouveau moteur de conception et de compilation pour ses architectures haut de gamme Arria 10 et Stratix 10.

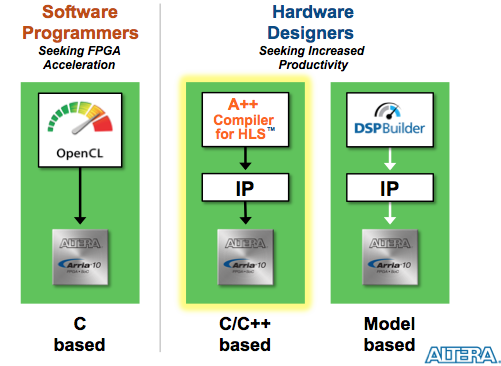

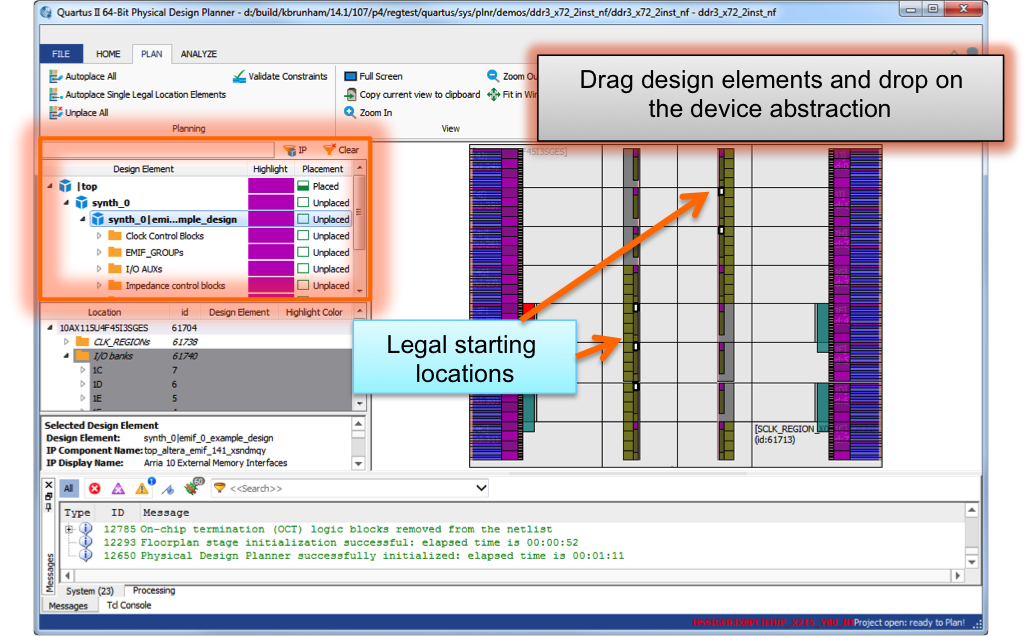

Baptisé Spectra-Q Engine, cet ensemble d’algorithmes est intégré dans la version 15.0 de l’environnement de développement Quartus II d’Altera. L’objectif avec ce moteur de calcul est triple. Il s'agit dans un premier temps de favoriser les conceptions à haut niveau, quel que soit le langage de conception utilisé (C, C++, OpenCL, modèles de haut niveau, langage HDL, langage A++ pour les compilations directes du C vers le HDL…), et ce grâce à une technologie de compilation à haut niveau d’abstraction. Spectra-Q Engine vise aussi à faciliter le travail d’intégration des blocs d’IP dans une conception (via des opérations simples de type “glisser-déposer”) et, enfin, à raccourcir significativement les temps de compilation.

La technologie logicielle mise en œuvre va notamment permettre de réaliser des conceptions incrémentales sans avoir à recompiler l’ensemble d’un design. Grâce, en particulier, à une base de données hiérarchique qui autorise la préservation des informations de placement et routage de blocs d’IP, alors même que le concepteur travaille à des modifications du design global.

La technologie logicielle mise en œuvre va notamment permettre de réaliser des conceptions incrémentales sans avoir à recompiler l’ensemble d’un design. Grâce, en particulier, à une base de données hiérarchique qui autorise la préservation des informations de placement et routage de blocs d’IP, alors même que le concepteur travaille à des modifications du design global.

Au-dessus de ce moteur de calcul, Altera propose dans le même temps la plate-forme de conception BluePrint qui ouvre la voie, pour une application donnée, à une exploration architecturale de la conception, intégrant l’analyse de l’assignation des interfaces entre les divers blocs d’IP utilisés. L’idée sous jacente est ici de réduire le nombre d’itérations nécessaires avant que le concepteur se fixe sur une option de design. Pour y parvenir, est notamment proposé un outil de prépositionnement des circuits d’horloge et des blocs de calcul au sein du design.

-fr.jpg)