Spécialiste des outils de vérification à destination des développeurs de processeurs à cœurs RISC-V, la firme britannique Imperas Software a étoffé ses solutions VIP (RISC-V Verification IP) avec des suites de tests de validation d’architectures RISC-V à virgule flottante. ...Les outils mis en avant couvrent les spécifications RISC-V 32 bits simple précision (32F), 64 bits simple précision (64F) et 64 bits double précision (64D), toutes conformes à la norme arithmétique IEEE 754-2008. L’objectif avec ces suites de test et de vérification est de détecter le plus tôt possible des bogues de conception, et d’éviter les coûts associés lorsque ces même bogues sont découverts plus tard.

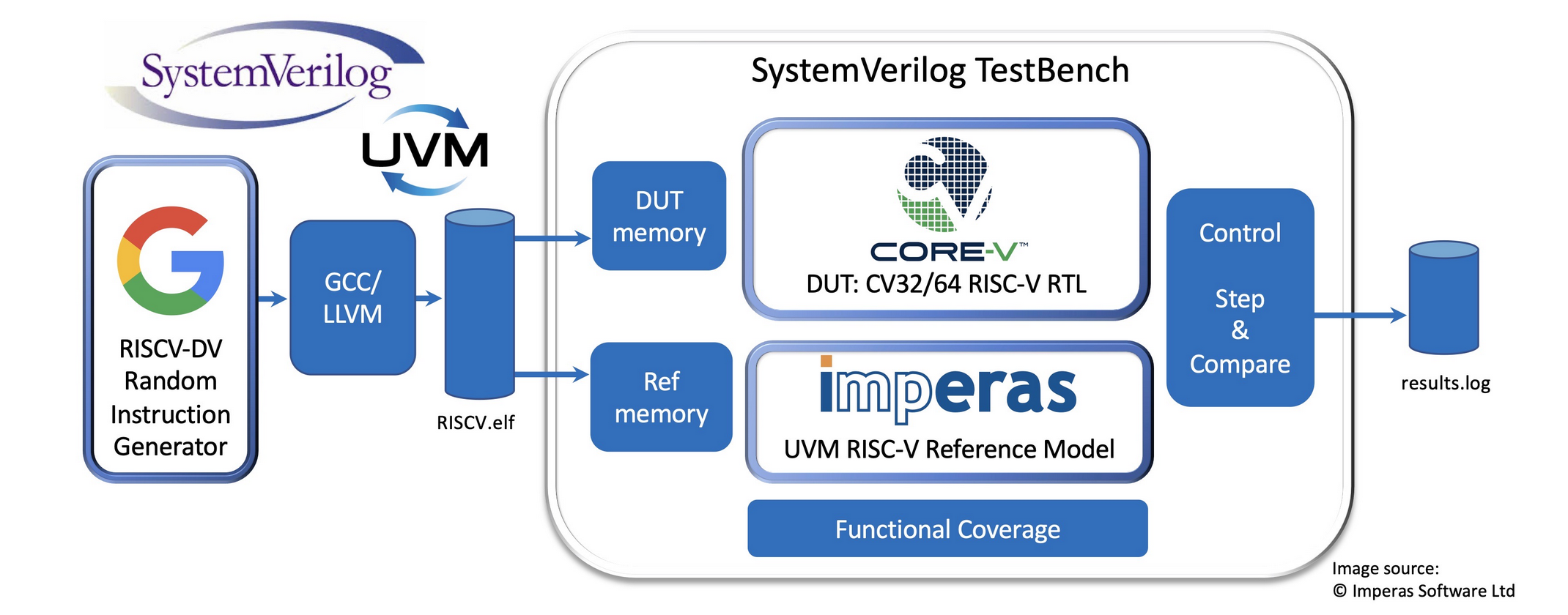

La méthodologie de vérification dite “step-and-compare” mise au point par Imperas permet par exemple de vérifier l’implantation d’un processeur décrit en langage RTL par rapport au modèle de référence stable (golden reference) mis à disposition des développeurs par Imperas, et encapsulé dans un environnement UVM (Universal Verification Methodology). Une méthodologie de vérification universelle normalisée pour vérifier les conceptions de circuits intégrés, écrite en SystemVerilog. Cette approche couvre l’analyse des événements asynchrones et offre une transition transparente et rapide vers l'analyse de débogage lorsqu'un problème est détecté.

La méthodologie de vérification dite “step-and-compare” mise au point par Imperas permet par exemple de vérifier l’implantation d’un processeur décrit en langage RTL par rapport au modèle de référence stable (golden reference) mis à disposition des développeurs par Imperas, et encapsulé dans un environnement UVM (Universal Verification Methodology). Une méthodologie de vérification universelle normalisée pour vérifier les conceptions de circuits intégrés, écrite en SystemVerilog. Cette approche couvre l’analyse des événements asynchrones et offre une transition transparente et rapide vers l'analyse de débogage lorsqu'un problème est détecté.

Pour prendre en charge l'encapsulation SystemVerilog du modèle de référence, le package Imperas RISC-V Processor Verification IP (VIP) comprend des exemples de composants et de modules prenant en charge SystemVerilog pour l'interfaçage et la synchronisation entre le modèle de référence Imperas RISC-V et le noyau RTL testé dans un flux de vérification pas à pas.

Pour rappel, les suites de tests Imperas sont destinées à la validation de la conformité architecturale d’un cœur RISC-V avec ses jeux d’instructions (ISA), et ne sont pas des suites de tests de vérification de conceptions matérielles complètes qui prouvent que le matériel est exempt de bogues.

Dans ce cadre, la couverture est un aspect clé de tout plan de vérification, car elle permet de mesurer les progrès vers les objectifs de qualité pour l'achèvement de la conception. Pour prendre en charge les instructions et la couverture fonctionnelle architecturale, le modèle de référence RISC-V “en or” d’Imperas a été dans le même temps amélioré avec des moniteurs intégrés pour fournir des mesures de couverture sans nécessiter de traitement post-simulation.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)