La société tchèque Codasip, qui propose des IP de processeurs embarqués RISC-V destinées aux concepteurs de puces-systèmes SoC, a été hissée par Western Digital au rang de fournisseur privilégié de packages de mise en œuvre matérielle du cœur RISC-V SweRV Core EH1 de l’Américain ...et de l’expertise technique associée. Disponible en open source depuis la fin 2018, ce cœur est notamment soutenu par l’alliance Chips au sein de la fondation Linux, qui vise à développer dans le cadre d’un environnement collaboratif un jeu de blocs d’IP et d’outils open source facilitant la conception de processeurs et de puces-systèmes SoC bâtis sur l’architecture RISC-V. Et ce sur des marchés aussi divers que les terminaux mobiles, l’informatique, l’électronique grand public et l’Internet des objets (lire notre article ici).

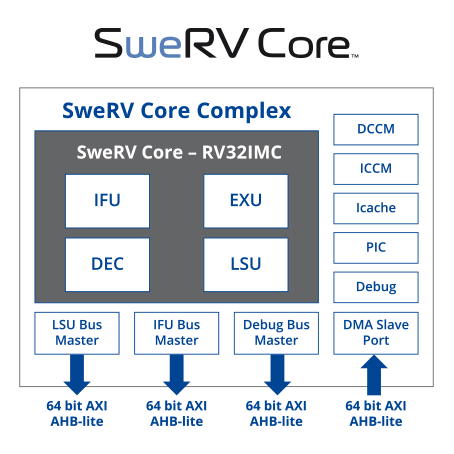

Décrit comme un cœur 32 bits superscalaire de degré 2, le SweRV Core EH1 est doté d’un pipeline de neuf étages qui permet le chargement et l’exécution de plusieurs instructions simultanément. Avec une performance de 4,9 CoreMark/MHz, il peut être cadencé à une fréquence maximale de 1,8 GHz une fois gravé en technologie Cmos 28 nm et cible de nouvelles applications orientées données dans les domaines des contrôleurs de stockage, de l’Internet des objets industriel, de l’analyse temps réel au sein de systèmes de surveillance, etc.

Décrit comme un cœur 32 bits superscalaire de degré 2, le SweRV Core EH1 est doté d’un pipeline de neuf étages qui permet le chargement et l’exécution de plusieurs instructions simultanément. Avec une performance de 4,9 CoreMark/MHz, il peut être cadencé à une fréquence maximale de 1,8 GHz une fois gravé en technologie Cmos 28 nm et cible de nouvelles applications orientées données dans les domaines des contrôleurs de stockage, de l’Internet des objets industriel, de l’analyse temps réel au sein de systèmes de surveillance, etc.

Dans le cadre de sa coopération avec Western Digital, Codasip fournit le SweRV Support Package (SSP) qui intègre tous les composants nécessaires à la conception, l’implémentation, les tests et la programmation logicielle d’une puce-système architecturée sur le cœur RISC-V SweRV Core, y compris les bancs d'essai de vérification et la propriété intellectuelle, les scripts de référence pour les principaux flots de conception électronique (CAO), des modèles de simulation et d'émulation et des outils de développement logiciel.

« Codasip s’est associé à Western Digital pour faciliter l'adoption de SweRV dans des puces produites en volume, indique Karel Masařík, le CEO de la firme tchèque. Le SweRV Core EH1 associe performances convaincantes et éco-efficacité énergétique, et avec notre SSP, les utilisateurs peuvent implémenter en toute confiance le SweRV Core dans leur puce-système à une fraction du coût des technologies concurrentes. » Le SSP, ainsi que les services optionnels de support technique, seront disponibles sous licence auprès de Codasip au cours du premier trimestre 2020.

Rappelons que Western Digital a participé à la levée de fonds de 10 millions de dollars bouclée par Codasip fin 2018 (lire notre article ici).

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)