La société BrainChip qui a développé sous la forme d’un bloc d’IP un processeur neuromorphique numérique destiné à insérer des traitements d’intelligence artificielle (IA) dans des puces-systèmes (SoC ) à mis en oeuvre la coexistence de sa technologie au sein d’un des coeurs RISC-V de la société Andes Technology, un spécialiste de cette architecture de processeur.

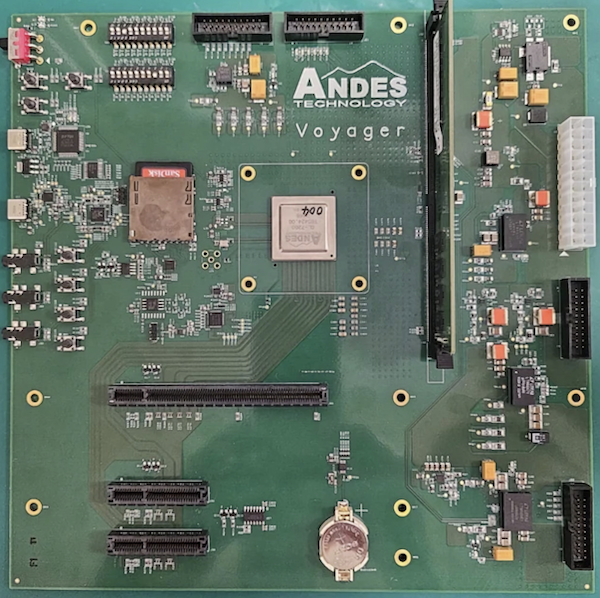

L'opération a consisté à associer la technologie Akida de BrainChip, sous la forme ici d’un module PCI Express au format M.2, récemment lancé par Brainchip, installé sur la carte de développement Voyager d’Andes sur laquelle on trouve un SoC à architecture RISC-V 64 bits de la société.

Plus précisément, il s’agit ici du circuit QiLai d’Andes (AndesCore AX45MP) et de la puce Akida (référencée AKD1500) de Brainchip fabriquée en technologie SOI en 22 nm insérée dans un modules M.2, l’ensemble étantinstallé sur la carte Voyager.

L’objectif affiché ici par les deux sociéts est d’accélérer le développement et le portage d'applications de grande envergure développées sous RISC-V avec en outre un calcul intégré d’IA en vue d’enrichir l'écosystème RISC-V.

Concrètement, la puce d’Andes avec la propriété intellectuelle du processeur multicœur 64 bits de la société est intégrée à la carte Voyager de la société associé à un calcul d’algorithmes d’IA réalisé par le circuit AKD1500 de Brainchip, économe en énergie, fondé sur les événements. Une technlogie utilisée avec des capteurs notamment pour des application dans l’automobile et les applications de sécurité.

Concrètement, la puce d’Andes avec la propriété intellectuelle du processeur multicœur 64 bits de la société est intégrée à la carte Voyager de la société associé à un calcul d’algorithmes d’IA réalisé par le circuit AKD1500 de Brainchip, économe en énergie, fondé sur les événements. Une technlogie utilisée avec des capteurs notamment pour des application dans l’automobile et les applications de sécurité.

Pour rappel, l’AKD1500 procure plus de 0,7 TOPS de puissance de calcul événementiel tout en consommant moins de 250 mW, atteignant des performances comparables au traitement des réseau de neurone conventionnel (CNN, réseaux de neurones convolutifs) avec une consommation, à puissance de calcul égale, de 3 à 10 fois inférieure.

En d’autres termes, il s’agit de démontrer ici qu’il est possible de concevoir une solution économique et économe en énergie pour l'intégration de SoC RISC-V fonctionnant à une fraction de la puissance requise par les accélérateurs d'IA traditionnels.

Fabriquée dans un process en 28 nm chez le fondeur TSMC et architecturée autour d’un cœur Arm Cortex-M4 et d’une matrice neuronale à 80 unités élémentaires de traitement, ce Soc de Branchip, grâce au module M.2, peut être connecté à n'importe quel processeur ou microcontrôleur à travers un bus USB ou PCI tout en bénéficiant de l'écosystème de développement logiciel qui l’accompagne.

Ce processeur neuronal consomme intrinsèquement, selon lBrainchip, moins d'énergie que les accélérateurs de réseaux neuronaux classiques. Le bloc d'IP prend en charge l'apprentissage incrémental et l'inférence à haute vitesse dans une grande variété de cas d'utilisation, tels que les réseaux neuronaux convolutionnels avec un débit élevé et des hautes performances pour une faible consommation. Procurant de fait, une efficacité énergétique et des performances élevées pour fournir des solutions d'IA jusqu'alors impossibles à réaliser sur des appareils embarqués en périphérie fonctionnant sur batterie ou sans ventilateur.

Pour rappel également, la puce QiLai d’Andes intègre un cluster RISC-V AX45MP à quatre coeurs superscalaire doté d’une mémoire cache de niveau 2 partagé, d'un gestionnaire de cohérence et d'une unité de gestion de la mémoire (MMU) pour la prise en charge des applications sous Linux.

Grâce à une interface IOCP (I/O completion ports, port de cohérence d’entrées/sorties) l'AX45MP permet à un DMA (Direct Memory Access) matériel externe d'interagir directement avec le sous-système cache/mémoire pour la communication entre l'AX45MP et des modules haut débit tels que des processeurs neuronaux (NPU, Neural Processing Unit), des GPU (Graphical Processing Unit) et le Gigabit Ethernet. L'AX45MP atteint des fréquences d'horloge allant jusqu'à 2,2 GHz sur le SoC QiLai fabriqué en 7 nm.

« Nous cherchons constamment à accroître l'adoption des solutions RISC-V dans un nombre croissant de cas d’utilisation, précise Charlie Su, directeur technique et président d'Andes Technology. En collaborant avec BrainChip et en intégrant la propriété intellectuelle Akida à notre plateforme QiLai Voyager, nous proposons aux développeurs une opportunité pour développer des solutions RISC-V optimisées pour les charges de travail et les capacités de l'IA en périphérie de réseau.»

-fr.jpg)