C’est lors du salon CES 2026 qui s’est tenu à Las Vegas du 9 au 12 janvier dernier que le fournisseur de semi-conducteurs américain Texas Instruments a dévoilé plusieurs technologies de traitement embarqué et analogiques dans une voiture qui permettent à la fois une prise de décision grâce à l’intelligence artificielle (IA) plus rapide et plus efficace, une perception précoce et précise de l’environnement d’un véhicule en mouvement, et une gestion des flux de données grâce à un réseau embarqué unifié.

Concrètement, il s’agit en premier lieu de la prise en charge de l’autonomie jusqu’au niveau 3 d’une voiture, définie par la SAE (Society of Automotive Engineers), grâce à la famille de puces systèmes (SoC) de calcul haute performance TDA5 de TI, compatible avec la technologie des chiplets y compris le support de de l’interface UCIE (Universal Chiplet Interconnect Express). Une approche qui permet aux concepteurs de mettre en œuvre un ensemble de fonctionnalités liées à plusieurs domaines à partir d’un seul circuit.

Ce dernier, disponible en volume à la fin de l'annés 2026, procurera des performances d’IA embarquées allant de 10 à 1 200 TOPS (billions opérations par seconde) avec une efficacité énergétique supérieure à 24 TOPS/Watt. Des performances à même de faciliter la prise en charge des milliards de paramètres dans les modèles de langage et les réseaux de transformateurs, augmentant ainsi la puissance de l’IA embarquée tout en maintenant une fonctionnalité interdomaine, c’est à dire la fusion des systèmes ADAS, des systèmes d’infotainment embarqués et des systèmes de passerelle dans une seule puce.

Celle-ci, dans les descriptions préliminaires fournies par TI, est dotée d’une unité de traitement neuronal, propre à TI, le NPU (Neural Procesor Unit) C7, de cœurs Arm Cortex-A720AE et d’une architecture axée sur la sécurité. Avec comme objectif d'autoriser les développeurs à déployer des systèmes ADAS plus sophistiqués sans avoir recours à des solutions thermiques coûteuses, selon TO.

Le TDA 5 dans sans première mouture le TDA 54-Q1 (qui fait partie des puces Jacienbto de TI) disposera de 8 coeurs Arm Cortex-A720AE flanqué de 6 coeurs Arm Cortex-R52+ pour le temps réel et de huit coeurs Arm Cortex-M55 pour la sécurité.

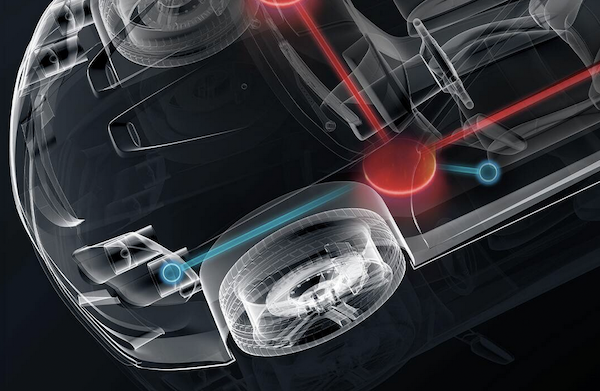

En second lieu, TI a dévoilé un nouvel émetteur-récepteur radar d’imagerie 4D cascadable, l’AWR2188, qui intègre jusqu’à huit émetteurs-récepteurs et huit récepteurs dans un seul boîtier. L’objectif ici, selon TI, est de simplifier avec une solution mon puce, la conception des radars embarqués dans les voitures par la prise en charge de cas d’utilisation avancés et l’adoption des architectures satellitaires, en vue d’une détection et d’une perception plus précoces des objets.

En second lieu, TI a dévoilé un nouvel émetteur-récepteur radar d’imagerie 4D cascadable, l’AWR2188, qui intègre jusqu’à huit émetteurs-récepteurs et huit récepteurs dans un seul boîtier. L’objectif ici, selon TI, est de simplifier avec une solution mon puce, la conception des radars embarqués dans les voitures par la prise en charge de cas d’utilisation avancés et l’adoption des architectures satellitaires, en vue d’une détection et d’une perception plus précoces des objets.

L’AWR2188 est doté d’un convertisseur analogique-numérique amélioré pour le traitement des données et d’un moteur spécifique our le traitement des signaux CHIRP (Compressed High-Intensity Radiated Pulse pour compression d'impulsion par modulation de fréquences) du radar. Ce niveau de performance autorise des cas d’utilisation radar avancés tels que la détection de cargaisons perdues, la distinction entre véhicules à proximité et l’identification d’objets dans des scénarios à haute performance dynamique. L’émetteur-récepteur peut en outre détecter des objets avec une plus grande précision à plus de 350 m de distance, favorisant ainsi une conduite plus sûre et autonome.

En troisième lieu, TI grâce au circuit de gestion de la couche physique d’Ethernet PHY Ethernet 10BASE-T1S DP83TD555J-Q1 qui se connecte à n'importe quel microcontrôleur à travers une interface SPI simple, a pour ambition d’accélérer l'adoption d'Ethernet aux nœuds périphériques des réseaux embarqués dans les véhicules. Avec à la clé une synchronisation temporelle à la nanoseconde, une fiabilité élevés et la prise en charge de l'alimentation par ligne de données (PoDL, Power over Dataline). Selon TI, l’accélération de la transition vers les SDV et des niveaux d’autonomie plus élevés entraîne un changement fondamental dans les architectures des sous-systèmes. L’Ethernet joue à ce niveau un rôle important catalyseur de cette évolution, car il permet aux systèmes de collecter et de transmettre en temps réel davantage de données dans les différentes zones du véhicule à travers une architecture réseau simple et unifiée.

En troisième lieu, TI grâce au circuit de gestion de la couche physique d’Ethernet PHY Ethernet 10BASE-T1S DP83TD555J-Q1 qui se connecte à n'importe quel microcontrôleur à travers une interface SPI simple, a pour ambition d’accélérer l'adoption d'Ethernet aux nœuds périphériques des réseaux embarqués dans les véhicules. Avec à la clé une synchronisation temporelle à la nanoseconde, une fiabilité élevés et la prise en charge de l'alimentation par ligne de données (PoDL, Power over Dataline). Selon TI, l’accélération de la transition vers les SDV et des niveaux d’autonomie plus élevés entraîne un changement fondamental dans les architectures des sous-systèmes. L’Ethernet joue à ce niveau un rôle important catalyseur de cette évolution, car il permet aux systèmes de collecter et de transmettre en temps réel davantage de données dans les différentes zones du véhicule à travers une architecture réseau simple et unifiée.

Dans ce cadre, le circuit DP83TD555J-Q1 de TI est doté d’un contrôleur d’accès support (MAC) intégré qui offre une synchronisation temporelle à la nanoseconde, une fiabilité optimale et des capacités PoDL (Power over Data Line). Des caractéristiques autorisant les ingénieurs d’étendre l’Ethernet hautes performances aux nœuds périphériques des véhicules tout en réduisant la complexité et les coûts de conception du câblage.

Pour rappel, l’Ethernet 10Base-T1S est conçu comme un réseau de prochaine génération apte à remplacer le CAN ou CAN FD dans les véhicules. La technologie utilise un câble à une seule paire torsadée, prévue pour transmettre des données à un débit de 10 Mbit/s dans des environnements automobiles où les niveaux de bruit et d’interférences électromagnétiques sont élevés. Avec le 10Base-T1S, les données sont transmises sur un seul canal à la fois, plutôt que d’utiliser plusieurs canaux comme dans une signalisation à large bande. Cette technologie est spécifiée par la norme IEEE 802.3cg sous sa forme à courte portée (15 mètres) adaptée au monde automobile.

Enfin, afin de simplifier la gestion complexe des logiciels embarqués, signalons que TI s’associe à l’éditeur de solutions de conception de circuits Synopsys pour fournir avec Virtualizer un kit de développement pour les SoC TDA5. Les capacités de jumeau numérique du kit autorise ici les ingénieurs à accélérer la mise sur le marché de leurs conceptions de véhicules définis par logiciel de plusieurs mois.

-fr.jpg)