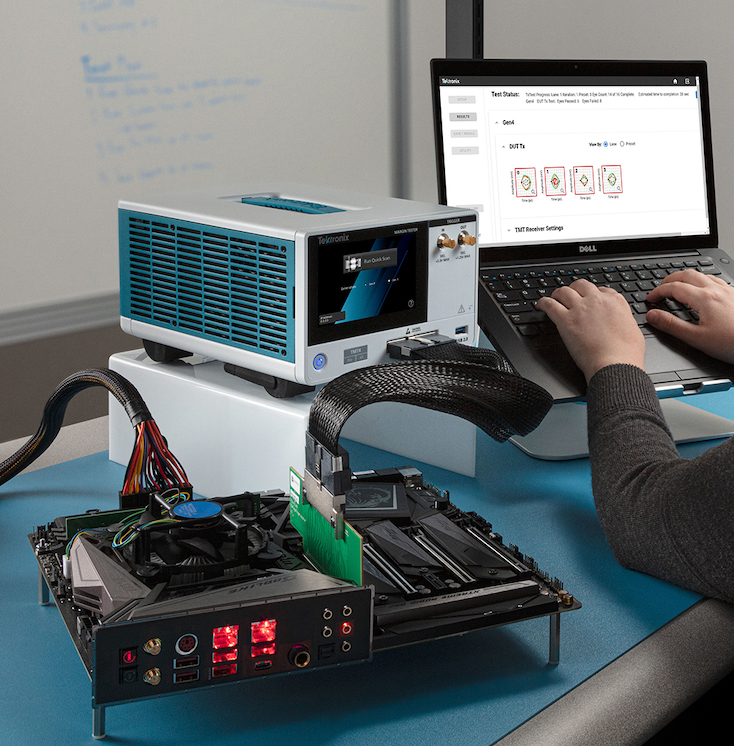

Le fournisseur d’instruments de test et mesure Tektronix annonce une solution de test d’une liaison PCI Express d'un nouveau genre avec le testeur de marge TMT4 qui, selon la société, révolutionne la mise en œuvre de ces procédures de test. Son interface tactile intégrée permet notamment de délivrer de premiers résultats en quelques minutes alors que jusqu'à présent, toujours selon Tektronix, la mise en œuvre et la réalisation des tests PCI Express prenaient des heures, voire des jours.

Concrètement, le Margin Tester TMT4 effectue des tests de marge et complète les solutions existantes que sont le testeur de taux d’erreur binaire (BERT, Bit Error Rate) ) et les oscilloscopes. Contrairement à ces deux instrument classiques, le nouvel appareil s’adresse à une population d’utilisateurs beaucoup plus large, avec des compétences moins pointues. Avec comme objectif de leur permettre de voir très rapidement si les systèmes à vérifier sont correctement configurés pour les tests et si, en première analyse, la “santé” de la liaison formée entre l’appareil et le système sous test est bonne, avec la pleine prise en charge du protocole Tx/Rx, des deux côtés de la liaison, dans un seul boîtier.

Cette capacité d’analyse en émission/réception permet notamment de repérer immédiatement des problèmes liés aux deux extrémités de la liaison PCI Express en utilisant un connecteur standard. Les tests d'émission des appareils testés fournissent des diagrammes de l'œil pour chaque combinaison mesurée, ainsi que les valeurs d'apprentissage du récepteur dont l’appareil s'est servi pour ouvrir le diagramme de l'œil affiché sur l’écran.

Cette capacité d’analyse en émission/réception permet notamment de repérer immédiatement des problèmes liés aux deux extrémités de la liaison PCI Express en utilisant un connecteur standard. Les tests d'émission des appareils testés fournissent des diagrammes de l'œil pour chaque combinaison mesurée, ainsi que les valeurs d'apprentissage du récepteur dont l’appareil s'est servi pour ouvrir le diagramme de l'œil affiché sur l’écran.

Quant au test de réception, il s’agit d’une évaluation fonctionnelle qui vise à déterminer dans quelle mesure l’amplitude du signal transmis par le testeur peut être réduite, dans une plage de fonctionnement prévue, avant que des erreurs ne soient renvoyées.

L’idée sous-jacente est d’améliorer le processus de développement d’une liaison PCIe afin d'identifier les problèmes au plus tôt, avant de faire appel à des solutions plus sophistiquées à base de testeur BERT et d’un oscilloscope. Dans ce cadre, le Margin Tester TMT4 ne remplace pas ces appareils qui réalisent l'ensemble des tests de validation et de conformité, mais les complète en accélérant la détection d’erreurs du processus de conception.

Ainsi, les ingénieurs quel que soit leur niveau d'expertise peuvent tester les dispositifs PCIe à travers quelque 160 combinaisons de liaisons et de préréglages en à peine 20 minutes, en utilisant la pleine vitesse du PCI Express Gen4. (Pour arriver à ce résultat, l’appareil intègre notamment un FPGA Stratix-10 d’Intel.)

Dans le détail, le Margin Tester TMT4 propose le mode Quick Scan qui permet d'évaluer l'état des liaisons pour les périphériques Gen3 ou Gen4, jusqu'à 16 voies, en quelques minutes. Dans cette analyse rapide, l’instrument et l'appareil testé font l'objet d'une négociation de liaison naturelle pour déterminer quels sont les préréglages à utiliser pour communiquer.

Le Margin Tester propose aussi le mode Custom Scan qui fournit des informations plus détaillées en permettant aux utilisateurs d'analyser les périphériques Gen3 ou Gen4, jusqu'à 16 voies, à travers les préréglages PCIe 0-9 (jusqu'à 160 combinaisons). Cette analyse personnalisée est destinée à fournir aux utilisateurs davantage de paramètres afin de prendre en charge des tests spécifiques et en forçant l'appareil testé à adopter des préréglages spécifiques vis-à-vis du test.

-fr.jpg)