Avec l’arrivée annoncée des cockpits automobiles de nouvelle génération combinant tableaux de bord 100% numériques, consoles centrales d’info-divertissement évoluées avec reconnaissance vocale et/ou gestuelle, ...affichage tête haute, écrans pour sièges arrière…, les fournisseurs de semi-conducteurs montent au créneau avec des processeurs hyperpuissants, dotés de fortes performances graphiques… et répondant néanmoins aux critères de sûreté et de sécurité imposés par le secteur automobile. C’est aujourd’hui NXP qui passe à l’attaque avec un premier jeu de circuits au sein de la nouvelle famille i.MX8, bâtis autour d’un maximum de six cœurs 64 bits à architecture ARMv8-A, d’un cœur de DSP HiFi 4 (d’origine Cadence), d’une double interface Gigabit Ethernet (avec fonctions AVB) et de ports mémoire LPDDR4 et DDR4.

Aptes à gérer jusqu’à quatre écrans HD indépendants ou un seul afficheur 4K, les i.MX8 que NXP compte échantillonner au cours du premier trimestre 2017 se déclinent selon trois modèles. L’i.MX 8QuadMax intègre deux cœurs ARM Cortex-A72, quatre cœurs Cortex-A53, deux cœurs de microcontrôleurs Cortex-M4F et deux unités graphiques GPU GC7000XS/VX (d’origine Vivante). L’i.MX 8QuadPlus s’appuie pour sa part sur un Cortex-A72, quatre Cortex-A53, deux Cortex-M4F et deux unités graphiques GC7000LiteXS/VX. Enfin l’i.MX 8Quad embarque quatre Cortex-A53, deux Cortex-M4F et deux unités graphiques GC7000LiteXS/VX.

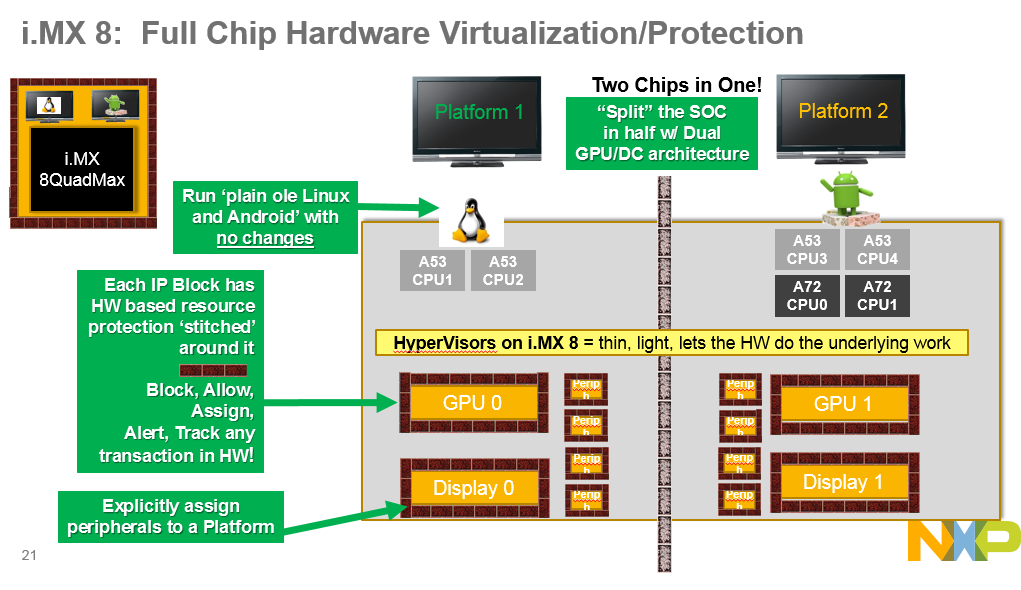

Cette nouvelle famille se caractérise aussi par ses mécanismes de virtualisation et de protection des ressources directement câblés dans le silicium, ajoute le fabricant de semi-conducteurs (voir illustration ci-dessous). Ainsi, assure NXP, chaque IP, des GPU aux ports série, ne peut être accédée que par le système d’exploitation auquel elle a été assignée, une caractéristique qui améliorerait la fiabilité de la plate-forme et réduirait les risques inhérents associés aux techniques de partage purement logicielles. Les différents OS amenés à s’exécuter sur un i.MX8 pourraient alors être déployés « out of the box » en utilisant l’architecture de répartition associée aux GPU et aux contrôleurs d’écran au sein du processeur, avec assignation d’un GPU et d’un contrôleur d’écran à chaque OS et garantie de performances déterministes.

Les i.MX8 supportent par ailleurs jusqu’à seize domaines séparés par des pare-feu et conçus pour isoler des pannes logicielles, des attaques malveillantes ou d’autres problèmes système. Enfin, grâce aux contrôleurs d’écran affublés de la fonction SafeAssure Fail-Over, il serait toujours possible de rerouter automatiquement les données d’affichage vers un pipeline graphique totalement isolé si une panne est détectée. Les utilisateurs pourront alors continuer de visualiser les informations critiques sur chaque écran, même si le processeur est relancé, assure NXP. Du coup, même si le sous-système d’info-divertissement (ou un autre sous-système connecté) est compromis, les mécanismes matériels de partitionnement seraient aptes à garantir que les autres sous-systèmes du cockpit numérique (et notamment les écrans affichant des informations critiques) continuent de fonctionner.

Les processeurs i.MX8 embarquent en outre un arsenal de technologies de sécurité et notamment un boot crypté, un algorithme de chiffrement par courbes elliptiques, le stockage sécurisé des clés de chiffrement et le support de standards de cryptographie tels que AES ou SHE, le tout dans un circuit qualifié AEC-Q100 Grade 3.

-fr.jpg)