L’architecture de processeur open source RISC-V attire les fournisseurs d’IP comme la lumière les papillons de nuit. La société belge Silex Insight, anciennement connue sous le nom de Barco Silex et spécialiste des blocs d’IP d’encodage/décodage vidéo et de sécurité, s’est ainsi fendu d’un communiqué pour indiquer que son portefeuille d’IP de sécurité eSecure était aussi disponible pour les conceptions d’Asic, de FPGA et de puces-systèmes SoC bâties autour de cœur(s) RISC-V. ...

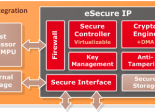

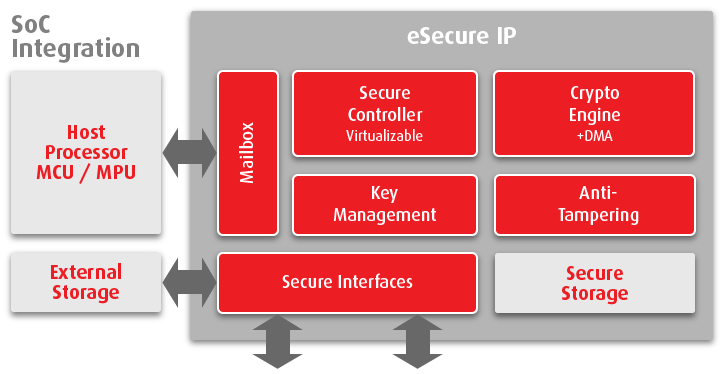

Avec eSecure, Silex Insight propose un ensemble modulaire de blocs d’IP qui, agissant en tant que racine de confiance (root-of-trust), sont censés garantir l’authenticité et l’intégrité du matériel, du logiciel, des données et du canal de communication de n’importe quel équipement connecté. Selon la société belge, la solution eSecure permet de réaliser toutes les opérations de sécurisation au niveau hardware et peut être mise à l’échelle en fonction des besoins de l’application. On y trouve un microcontrôleur sécurisé, qui assure le contrôle de toutes les fonctions de sécurité et notamment celles isolant les secrets du processeur hôte (comme les clés de chiffrement) des applications, ainsi qu’un moteur de cryptographie qui prend en charge les algorithmes les plus récents comme TLS/DTLS 1.3 et les mécanismes spécifiés par les protocoles Thread, HomeKit (Apple), Bluetooth ou ZigBee.

Avec eSecure, Silex Insight propose un ensemble modulaire de blocs d’IP qui, agissant en tant que racine de confiance (root-of-trust), sont censés garantir l’authenticité et l’intégrité du matériel, du logiciel, des données et du canal de communication de n’importe quel équipement connecté. Selon la société belge, la solution eSecure permet de réaliser toutes les opérations de sécurisation au niveau hardware et peut être mise à l’échelle en fonction des besoins de l’application. On y trouve un microcontrôleur sécurisé, qui assure le contrôle de toutes les fonctions de sécurité et notamment celles isolant les secrets du processeur hôte (comme les clés de chiffrement) des applications, ainsi qu’un moteur de cryptographie qui prend en charge les algorithmes les plus récents comme TLS/DTLS 1.3 et les mécanismes spécifiés par les protocoles Thread, HomeKit (Apple), Bluetooth ou ZigBee.

Dans une implémentation typique sur puce-système SoC, eSecure se comporte comme un coprocesseur de sécurité qui décharge le processeur principal des calculs cryptographiques et évite l’indisponibilité temporaire de l’application principale, précise Silex Insight.

A noter que d’autres fournisseurs d’IP de sécurité se sont récemment positionnés au sein de l’écosystème RISC-V à l’instar d’Inside Secure et de Rambus. La fondation RISC-V, l’organisme industriel qui promeut l’adoption de l’architecture du même nom, a par ailleurs formé un comité chargé d’établir un consensus autour des meilleures pratiques de sécurité et d’identifier les améliorations potentielles à apporter à la sécurité des objets connectés, des systèmes embarqués et des implémentations d’apprentissage automatique architecturés autour de circuits RISC-V (lire notre article ici).

-dissolve-basic-fr.jpg)