L’organisme PCI-SIG, en charge de l'évoution du bus série PCI Express, vient de publier la spécification PCIe 7.0 afin de répondre aux besoins en bande passante pour les applications fondées sur l’utilisation d’algorithmes d’intelligence artificielle (IA), et ce en vue d’ atteindre des débits de transfert jusqu’à 128 Giga Transferts/s.

Cette spécification PCIe 7.0 cible les applications pilotées par les données, notamment l’IA et le ML (Machine Learning), l'Ethernet 800G, le cloud computing et l'informatique quantique.

Pour atteindre de tels débits, le PCI SIG indique que la fréquence de signalisation physique du PCIe 7.0 sera poussée à 32 GHz, contre 16 GHz pour les versions 5.0 et 6.0. Une première hausse depuis 2017. Mais plus la fréquence augmente, plus il devient difficile de maintenir l’intégrité du signal sur des câbles en cuivre - problèmes d’atténuation, d’interférences électromagnétiques, de diaphonie.

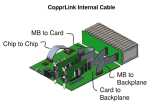

C’est pourquoi, le PCI SIG publie dans le même temps une révision de sa spécification d'interconnexion optique conçue pour améliorer les performances de la technologie PCI Express dans les centres de données. Le document intitulé ECN (Engineering Change Notice ) nommé Optimal Aware Retimer modifie les spécifications PCIe 6.4 et 7.0 pour y intégrer une solution standardisée autour d’un retimer PCIe optique.

Dans le détail, le document ECN de resynchronisation du PCIe permet notamment l'interconnexion transparente de diverses technologies optiques entre commutateurs et points de terminaison, conformément aux spécifications PCIe 6.4 et 7.0. Une approche qui ouvre la voie, selon le PCI SIG, à la première méthode standardisée de l'industrie pour la mise en œuvre de la technologie PCI Express sur fibre optique.

« Nous avons identifié le besoin d'une interconnexion optique standard fondée sur la technologie PCIe, et la technologie de resynchronisation optique constitue la première étape vers une solution optique modulaire, précise Al Yanes, le président du PCI-SIG. Nous prévoyons une adoption initiale dans les applications au sein des centres de données pour gérer l’IA et l’apprentissage automatique (Machine Learning). Avec la généralisation de la technologie PCIe, nous anticipons aussi dans le même temps des cas d'utilisation innovants sur de nombreux autres segments de marché. »

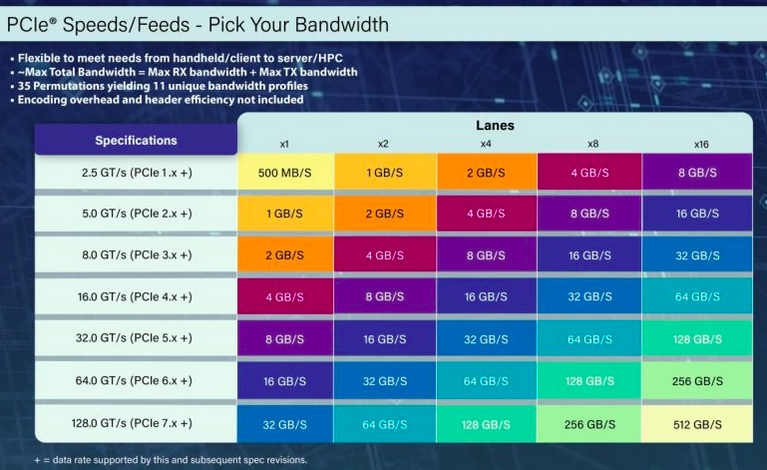

Parallèlement, le PCI SIG indique que la définition de la spécification PCIe 8.0 est déjà en cours d'écriture afin de soutenir les investissements et les feuilles de route de l'écosystème technologique du PCIe qui procure dans sa version 7.0, sur le papier, un débit binaire brut de 128 Giga Transferts/s et jusqu'à 512 Go/s en mode bidirectionnel (à travers une configuration x16).

Parallèlement, le PCI SIG indique que la définition de la spécification PCIe 8.0 est déjà en cours d'écriture afin de soutenir les investissements et les feuilles de route de l'écosystème technologique du PCIe qui procure dans sa version 7.0, sur le papier, un débit binaire brut de 128 Giga Transferts/s et jusqu'à 512 Go/s en mode bidirectionnel (à travers une configuration x16).

A noter que le PCIe 7.0 utilise la signalisation PAM4 (Pulse Amplitude Modulation 4 levels) pour une meilleure efficacité énergétique et une rétrocompatibilité assurée avec les générations précédentes de technologie PCIe.

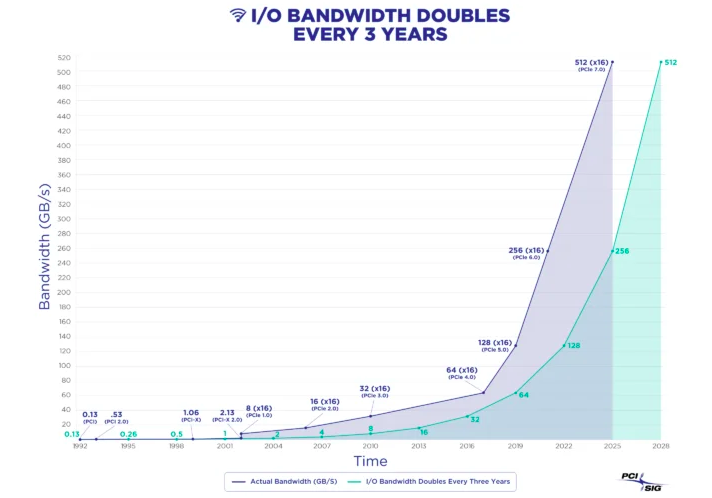

Le PCIE 7.0 s’inscrit ainsi dans la feuille de route décrétée par le PCI SIG qui vise à doubler la bande passante d’entrées/sorties du bus PCIe tous les trois ans.

Les centres de données seraient d’ores et déjà prêts à déployer des réseaux basés sur la technologie PCIe 7.0, et les fabricants d’Asic sont eux aussi engagés pour fournir des blocs d’IP conformes au standard PCIe 7.0.

Étant donné le temps qu'il a fallu plusieurs années pour que les produits compatibles PCIe 5.0 ne soient commercialisés, il faudra probablement à nouveau plusieurs années avant que le matériel PCIe 7.0 ne soit disponible, avec une arrivée concréte estimée entre 2o28 et 2029. Mais lorsque le PCIe 7.0 sera concrétement dispible, il sera dès lors possible d’atteindre des débits de données jusqu'à quatre fois supérieures à celle du PCIe 5.0 qui propose actuellement un débit binaire brut "limité" à 32 Giga Transferts/s ou 128 Go/s en transfert de données bidirectionnel (en configuration x16).

-fr.jpg)