[TRIBUNE de James Jeffs et Yu-Han Chang d'IDTechEx] Des ordinateurs sur roues. C'est ainsi que l’on perçoit actuellement les véhicules. Pratiquement tout ce qui se passe au sein d’une automobile est surveillé et actionné par un microcontrôleur, depuis l'ouverture des fenêtres jusqu'au calcul du mélange air-carburant optimal pour le couple moteur. Mais ce n’est que la partie émergée de l’iceberg alors que la puissance de calcul embarquée dans les véhicules augmente de façon exponentielle avec l’arrivée des véhicules dotés d’une autonomie de niveau 3 et des robotaxis. Dans ce cadre, les puces pour le calcul haute performance (HPC) mises en œuvre dans les automobiles devront s’appuyer sur de nouvelles approches technologiques. Eclairages de Yu-Han Chang et James Jeffs, Senior Technology Analysts de la société d’études IDTechEx.

Alors que s’ouvre l’ère des transports autonomes, de nouvelles exigences en matière de traitement embarqué se font jour dans l’industrie automobile. Les voitures automatisées nécessitent de vastes ensembles de capteurs pour analyser l’environnement et fournir les données dont le véhicule a besoin pour imiter la conduite humaine. Selon le rapport "Autonomous Cars and Robotaxis 2024-2044" d'IDTechEx, les principaux robotaxis dotés d’une automatisation de niveau SAE 4 disposent de jusqu'à 40 capteurs différents.

Avec le déploiement prochain de technologies automatisées sur le marché automobile, le marché des capteurs automobiles connaîtra une croissance moyenne de 13% par an sur les dix prochaines années. Toutefois les capteurs seuls sont pratiquement inutiles sans une capacité de calcul haute performance capable de traiter les données qu’ils produisent et de construire un rendu 3D de l'environnement pour éclairer la politique de conduite programmée du véhicule.

Le calculateur haute performance (HPC) récupère les données en temps réel provenant de l’ensemble des capteurs et exécute plusieurs processus importants. Les deux principaux défis auxquels il est confronté sont la fusion des capteurs et la classification des objets, et il existe un certain désaccord quant à l'ordre dans lequel ces tâches doivent être effectuées. Certains pensent qu'une fusion précoce est la meilleure solution. Ici toutes les données des capteurs sont combinées dans un rendu 3D de la scène, puis un algorithme d'intelligence artificielle (IA), exécuté par l'unité HPC du véhicule, identifie et étiquette chaque objet détecté. D'autres pensent qu'une liste d'objets devrait être générée à partir de chaque capteur, puis les résultats fusionnés. Cette approche présente l'avantage de pouvoir croiser les détections de chaque capteur et vérifier leur concordance. L’inconvénient réside cependant dans la difficulté de gérer les écarts entre les listes d’objets provenant de différents capteurs.

La puce-système SoC de traitement autonome

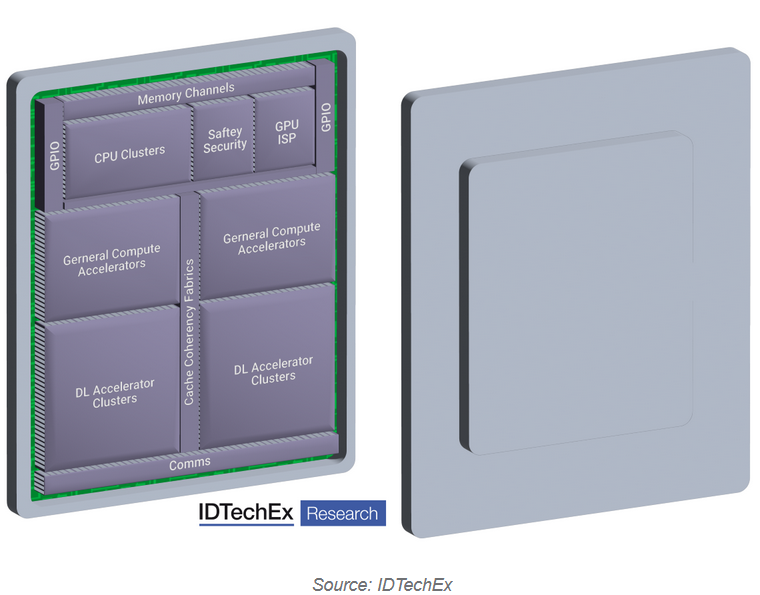

Que la fusion de données soit tardive ou précoce, le calculateur HPC a par ailleurs une grande quantité de calculs à réaliser sous forme de traitement d'images et d'exécution d'algorithmes IA pour la classification des images et la politique de conduite. Les composants clés qui gèrent ces tâches sont les processeurs graphiques (GPU), les processeurs généralistes (CPU) et la mémoire RAM. Il s'agit généralement de composants discrets distincts mais les exigences spécifiques du HPC pour les voitures autonomes ont conduit à les combiner sur des puces-systèmes SoC uniques. Celles-ci combinent des GPU, des CPU, de la RAM et bien d’autres sous-systèmes sur une seule puce de silicium.

Le SoC idéal peut recueillir les données de tous les capteurs de conduite autonome du véhicule, les traiter, identifier et classer tous les objets détectés et générer un ensemble d’actions liées à la direction, l’accélération et le freinage en fonction de la politique de conduite. Au global le SoC est responsable de l’ensemble du système de conduite autonome.

Mettre toutes ces fonctionnalités sur une seule puce est essentiel pour répondre aux exigences informatiques de la conduite autonome. Avec une séparation physique quasi nulle, chaque partie de la puce peut échanger des données avec une latence proche de zéro, avec un bruit minimal et une bande passante énorme.

Les GPU sont un élément clé du puzzle ; leurs capacités de traitement d’images, combinées à leur aptitude à exécuter des algorithmes IA via l’apprentissage profond et les réseaux de neurones, en font la pierre angulaire du SoC. C’est pourquoi nous voyons Nvidia gagner du terrain dans le domaine des véhicules autonomes. La société a une longue histoire dans le développement de GPU pour des applications graphiques en informatique et a su évoluer en apportant son expertise à l’industrie automobile. Ses plates-formes Xavier et Orin sont des incontournables du traitement informatique des véhicules autonomes.

Mobileye est un autre pionnier de cette industrie. Fondée en 1999, l’entreprise a rapidement fait impression et s'est fait un nom, suscitant l'intérêt d'Intel qui l’a finalement rachetée. Désormais à nouveau public, Mobileye a trouvé sa place dans de nombreux véhicules grand public en équipant des applications d’assistance évoluée à la conduite (ADAS).

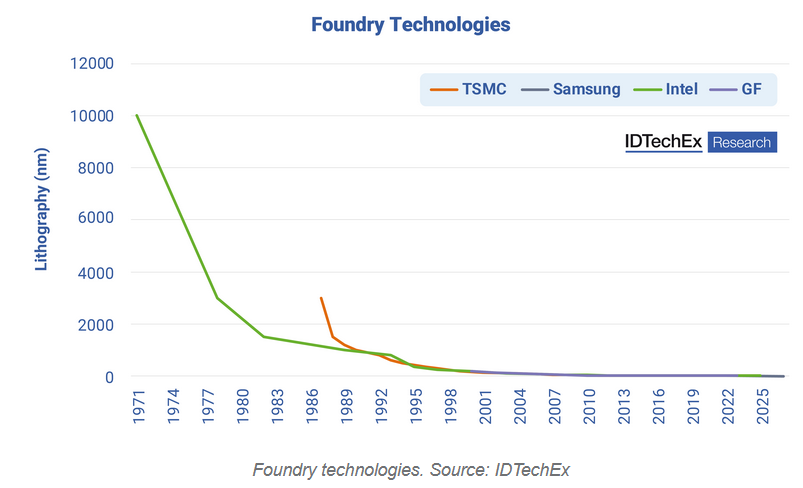

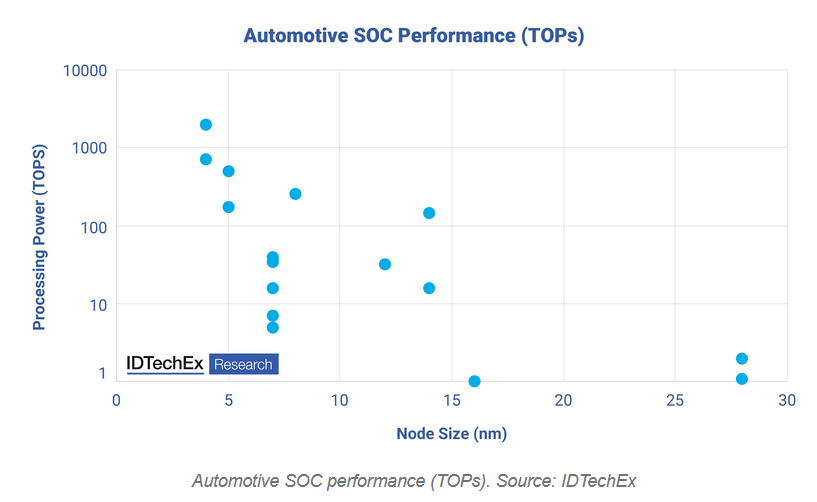

Mobileye et Nvidia ont récemment augmenté la puissance de calcul de leurs puces, passant de quelques téraopérations par seconde (Tops) à des dizaines voire des centaines de Tops, avec l’objectif d’atteindre des milliers de Tops. Ces améliorations tiennent pour une bonne part à l'adoption de procédés de gravure de plus en plus fins provenant de fonderies de premier plan comme TSMC et Samsung.

Des technologies de semi-conducteurs en pleine croissance

Ces dernières années, IDTechEx a vu Mobileye, Nvidia et d'autres passer entre 2018 et 2021 de solutions FinFET de 28 nm à 7 nm et moins. Cependant, les fonderies sont désormais capables de produire désormais des puces à des technologies inférieures à 5 nm et se dirigent vers des technologies inférieures à 1 nm.

IDTechEx a constaté que chaque fois que la technologie de gravure est réduite de moitié, la puissance de calcul augmente d'un facteur 10. Mais passer à des nœuds technologiques de plus en plus petits deviendra de plus en plus coûteux. Une seule tranche de 300 mm de technologie TSMC 3 nm coûte environ 20 000 dollars et ce prix continuera d'augmenter au fur et à mesure que des technologies inférieures à 3 nm seront exigées dans une variété d'industries, depuis les applications informatiques classiques telles que les téléphones, les ordinateurs portables et les PC, jusqu'aux nouvelles demandes provenant du secteur automobile.

En tant que tels, les développeurs HPC automobiles doivent réfléchir à la manière dont ils peuvent optimiser les technologies existantes pour obtenir le maximum de performances. L'une des approches envisagées par IDTechEx consiste à se concentrer davantage sur l'intelligence artificielle (IA), les réseaux de neurones (NN) et les accélérateurs d'apprentissage profond (Deep Learning). L’idée est de mettre en œuvre de nouvelles stratégies de traitement des données améliorées par l’IA, réduisant ainsi le recours aux approches classiques que l’on trouve dans les GPU. Cela peut améliorer les performances de la puce à moindre coût, en nécessitant moins d'investissement dans des technologies de nœuds plus petits et en produisant même un avantage global en matière d'efficacité.

IDTechEx constate que l'IA devient plus courante dans les diagrammes de blocs des puces-systèmes des principaux fournisseurs de niveau 2 comme Mobileye et Renesas. Mais une perspective particulièrement intéressante est celle de Recogni. Recogni est une start-up qui a développé un accélérateur IA pour les applications SoC de conduite autonome qui promet une puissance de calcul et une efficacité révolutionnaires.

Même avec la réduction de la taille des nœuds et des solutions IA imaginatives, l’industrie des puces de calcul dans son ensemble continue de constater un ralentissement du rythme de développement.

La loi de Moore stipule que la puissance de calcul devrait doubler tous les deux ans, une formule empirique vieille de plusieurs décennies et qui est restée valable jusqu'à récemment. Or certains disent que la loi de Moore commence à ralentir à mesure que l'industrie est confrontée à des défis technologiques de plus en plus difficiles pour réaliser des gains progressifs de plus en plus faibles. D’autres assurent que la loi de Moore est morte.

Une technologie émergente : les "chiplets"

Une solution importante pour faire face au ralentissement de la loi de Moore et à l'augmentation substantielle du coût de fabrication des circuits intégrés monolithiques est le concept de "chiplets". Le concept de base des chiplets consiste à déconstruire un circuit intégré monolithique en blocs fonctionnels distincts, à transformer ces blocs en chiplets séparés, puis à les réassembler au niveau du packaging. L'objectif ultime d'un processeur bâti sur des chipsets est de maintenir ou d'améliorer les performances tout en réduisant les dépenses globales de production par rapport aux circuits intégrés monolithiques traditionnels.

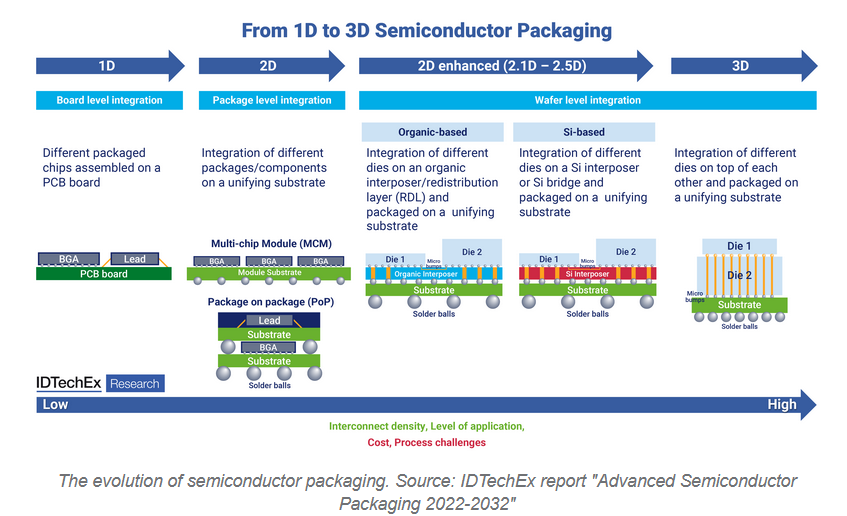

L'efficacité de la conception des chipsets repose largement sur les techniques de packaging, en particulier celles utilisées pour interconnecter plusieurs chiplets, car elles ont un impact significatif sur les performances système globales. Ces technologies avancées de conditionnement de semi-conducteurs, englobant des approches telles que les circuits intégrés 2,5D, les circuits intégrés 3D et le procédé d'encapsulation de puce au niveau tranche de sortance (Fan-Out Wafer-Level), sont collectivement appelées "conditionnement avancé de semi-conducteurs".. Ces techniques de pointe facilitent la convergence de plusieurs chiplets, souvent produits à différents nœuds de processus, sur un seul substrat. Cette convergence est rendue possible par l'utilisation de tailles de bossage compactes, permettant ainsi des densités d'interconnexion accrues et des capacités d'intégration supérieures.

S'inspirer du secteur informatique

Pour examiner le paysage actuel des technologies avancées de conditionnement de semi-conducteurs dans l’industrie, prenons le secteur des processeurs pour serveurs comme exemple illustratif. Alors que la plupart des processeurs pour serveurs contemporains sont construits autour de conceptions monolithiques de puces-systèmes, des développements notables ont émergé. En 2021, Intel a annoncé son prochain processeur pour serveur, Sapphire Rapids, qui adoptera une nouvelle approche.

Ce processeur de nouvelle génération sera construit sous la forme d'un module à quatre puces interconnectées via la technologie EMIB (Embedded Multi-Die Interconnect Bridge) d'Intel, représentant une solution avancée de conditionnement de semi-conducteurs 2,5D. Parallèlement, AMD a exploité la puissance des techniques avancées de conditionnement de semi-conducteurs 3D pour améliorer les performances des processeurs pour serveurs.

Dans le cas de sa dernière puce en date, référencée Milan-X et sortie en mars 2022, AMD utilise une stratégie de packaging 3D qui consiste à empiler une puce de cache directement au-dessus du processeur. Cette innovation se traduit par une augmentation de la densité d'interconnexion de plus de 200 fois par rapport au packaging 2D conventionnel, selon les affirmations d'AMD.

Ces développements ne se limitent pas aux seuls processeurs ; le domaine des centres de données a également été témoin de l'intégration de technologies avancées d’encapsulation de semi-conducteurs pour d'autres composants, tels que les accélérateurs. Nvidia, un acteur clé, utilise depuis 2016 la technologie de packaging 2,5D de TSMC connue sous le nom de Chip on Wafer on Substrate (CoWoS) pour ses accélérateurs GPU haut de gamme.

Cette vague d'adoption, illustrée par Intel et AMD dans leurs produits de pointe, indique une utilisation croissante des technologies avancées de packaging de semi-conducteurs dans l'ensemble du secteur. La tendance va au-delà des processeurs pour serveurs et englobe une variété de composants pour centres de données. À mesure que le paysage industriel évolue, ces méthodologies innovantes sont sur le point de jouer un rôle central dans l'amélioration des performances, de l'intégration et de l'efficacité.

Dans un avenir prévisible (sur une période de 10 à 15 ans), poussé par des exigences de traitement croissantes et la nécessité d'une bande passante importante pour une consommation d'énergie minimale, le secteur automobile imitera une trajectoire semblable à celle du cloud et du calcul haute performance (HPC). Cette trajectoire implique l’intégration de divers blocs d’IP et d’éléments silicium au niveau du boîtier pour atteindre des fonctionnalités essentielles et des performances optimales.

Dans le contexte des processeurs de traitement des véhicules autonomes, le paysage du packaging sera témoin de la fusion de plusieurs composants silicium au sein du même boîtier, mettant en œuvre des approches avancées de conception 2,5D et 3D. Avec la demande croissante de calcul haute performance dans les véhicules et la nécessité d’une croissance continue des performances, les technologies utilisées dans les calculateurs automobiles vont évoluer rapidement. Les tailles de nœuds technologiques inférieures à 3 nm, les conceptions à base de chiplets, le recours accru à l'accélération IA, le packaging 2,5D et même le packaging 3D deviendront tous des éléments traditionnels du HPC pour les technologies autonomes dans les voitures.