L’américain Lattice étend aujourd'hui la portée de ses architectures FPGA basse consommation avec la mise sur le marché de la famille des FPGA de contrôle MachXO5-NX, cinquième génération construite sur la plate-forme Nexus de la société.

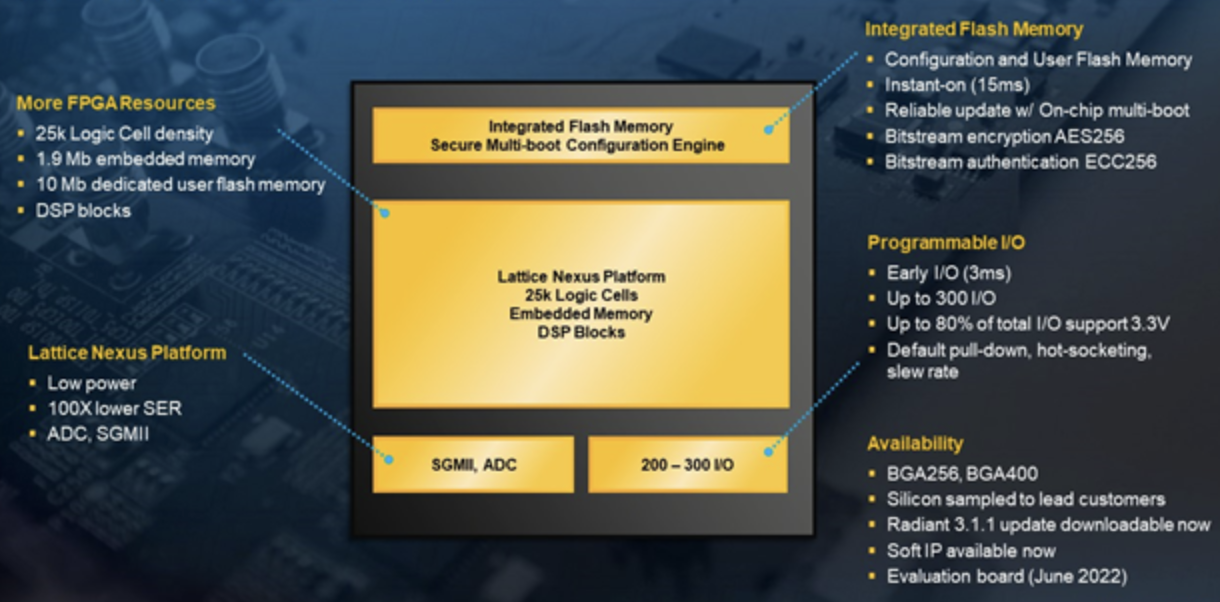

Pour rappel, la plate-forme Nexus tire parti des avantages de la technologie FD-SOI 28 nm (Fully Depleted Silicon On Insulator) pour produire des FPGA dotés de 10 à 200 000 cellules logiques à très faible consommation - jusqu'à 70 % inférieure à celle des FPGA concurrents de classe similaire avec une gestion thermique simplifiée et un coût d'exploitation total optimisé selon Lattice. La plate-forme intègre des blocs DSP optimisés et une capacité mémoire élevée qui permettent des rapports mémoire/logique adaptés aux applications complexes, comme l’intelligence artificielle (IA) embarquée.

Dans ce cadre, les FPGA MachXO5-NX combinent une structure FPGA d'une capacité de 25 000 cellules logiques avec 1,9 Mbits de mémoire intégrée, ce qui, selon Lattice, réduit l'empreinte des conceptions en minimisant le besoin de mémoire externe. Ces circuits offrent également jusqu'à 9,2 Mbits de mémoire flash destinée à stocker données utilisateur et paramètres critiques, autorisant la mise à disposition auprès des développeurs d’une solution à puce unique avec des mises à jour sur le terrain prenant en charge plusieurs images de configuration.

Ces FGA comportent jusqu'à 300 entrées/sorties à usage général (80% prenant en charge la signalisation 3,3 V) et offrent des fonctionnalités supplémentaires telles qu’un lien SGMII (Serial Gigabit Media-Independent Interface) à 1,25 Gbit/s pour la connexion à un réseau Fast Ethernet, une connexion à chaud, etc.

Ces FGA comportent jusqu'à 300 entrées/sorties à usage général (80% prenant en charge la signalisation 3,3 V) et offrent des fonctionnalités supplémentaires telles qu’un lien SGMII (Serial Gigabit Media-Independent Interface) à 1,25 Gbit/s pour la connexion à un réseau Fast Ethernet, une connexion à chaud, etc.

Côté sécurité, Lattice met en avant la présence d’une technologie multi-boot sur la puce avec fonctions de chiffrement (AES256) et d'authentification (cryptographie à courbes elliptiques ECC256) du bitstream.

Au-delà, tirant parti du processus de fabrication FD-SOI, ces FPGA affichent, selon Lattice, un taux d'erreurs logicielles jusqu'à 100 fois inférieur par rapport aux FPGA concurrents d'une classe similaire.

Les FPGA MachXO5-NX sont conçus pour améliorer la surveillance et le contrôle de systèmes sécurisés sur les marchés des serveurs, des communications, de l'industriel et de l'automobile.

« Les demandes croissantes de surveillance et de fiabilité des systèmes sécurisés nécessitent des capacités de contrôle système supplémentaires, explique Gordon Hands, directeur marketing produit de Lattice Semiconductor. Les utilisateurs recherchent à ce niveau des solutions pour répondre à ces exigences tout en augmentant l'efficacité de la conception et en simplifiant son intégration dans un système. »

-fr.jpg)