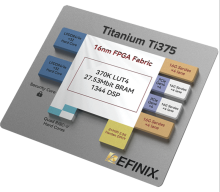

L’américain Efinix, concepteur de circuits logiques programmables, a profité de la caisse de résonance du salon Embedded World 2024 pour annoncer la disponibilité en accès anticipé de sa dernière puce en date, le Titanium Ti375.

Ce FPGA, qualifié AEC-Q100 Grade 1 pour le marché automobile et fabriqué dans un procédé de gravure 16 nm de TSMC, est doté de 375 000 éléments logiques, d’un processeur RISC-V 32 bits à quatre cœurs cadencés à 1 GHz (gravé dans le silicium), d’un contrôleur mémoire LPDDR4, d’une interface Mipi D-PHY pour la connexion à des écrans ou à des caméras, et de quatre banques d’émetteurs-récepteurs SerDes à 16 Gbit/s pour la prise en charge des interfaces PCIe Gen4 et 10 Gigabit Ethernet.

Le Titanium Ti375 est également livré avec 1 344 blocs de traitement DSP, 2 688 blocs de mémoire SRam de 10 Ko et 27,53 Mbits de mémoire intégrée, ainsi qu'avec des blocs DSP optimisés pour les charges de travail lourdes liées au traitement des algorithmes d’intelligence artificielle (IA). Les émetteurs-récepteurs Quad SerDes prennent en charge des débits de données bruts allant jusqu'à 16 Gbit/s avec plusieurs protocoles, y compris le PCIe 4.0, l’Ethernet SGMII (Serial Gigabit Media-Independent Interface) et l’Ethernet 10GBase-KR (pour les communications en fond de panier).

Le mécanisme de virtualisation SRIOV (Single Root I/O Virtualization) et les doubles contrôleurs DRam LPDDR4/4X sont aussi supportés en vue d’obtenir une bande passante élevée.

« La famille des FPGA Titanium établit une nouvelle référence pour nous sur le marché de l'imagerie, commente Jan Hartmann, directeur général du fabricant allemand de caméras industrielles IDS Imaging Development Systems. Grâce notamment aux interfaces SerDes présentes et aux capacités de calcul à haute vitesse liées à la logique programmable et aux cœurs RISC-V. »

-fr.jpg)