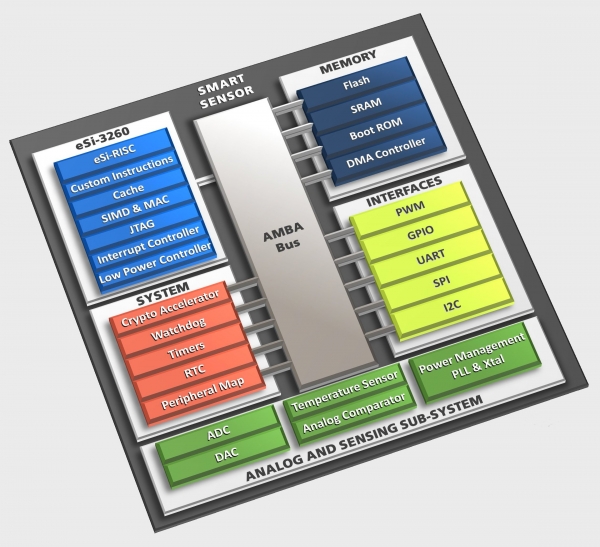

Le britannique EnSilica vient d’étoffer sa gamme de cœurs de processeurs logiciels eSi-Risc avec l’eSi-3260, plus particulièrement destiné aux nœuds de capteurs de l’Internet des objets, aux écrans avec détection de touchers ...ou de gestes et aux applications éco-énergétiques toujours connectées. Ce modèle, qui conserve les caractéristiques de compacité et de très faible consommation de la famille eSi-Risc, se distingue par le support de fonctionnalités DSP grâce à l’intégration d’une unité MAC (multiplication-accumulation) de précision 64 bits, apte notamment à effectuer quatre multiplications et deux additions par cycle.

Selon EnSilica, le cœur eSi-3260 à cinq niveaux de pipeline a été optimisé pour un fonctionnement à des fréquences de plus de 1 GHz en technologie de gravure 28 nm. Il affiche alors une consommation de 14 µW/MHz qui peut être abaissée à 3 µW/MHz si l’on adapte le processeur pour une sobriété réduite au minimum, plutôt que pour un fonctionnement à fréquence maximale.

Selon EnSilica, le cœur eSi-3260 à cinq niveaux de pipeline a été optimisé pour un fonctionnement à des fréquences de plus de 1 GHz en technologie de gravure 28 nm. Il affiche alors une consommation de 14 µW/MHz qui peut être abaissée à 3 µW/MHz si l’on adapte le processeur pour une sobriété réduite au minimum, plutôt que pour un fonctionnement à fréquence maximale.

Le cœur se distingue aussi par une architecture mémoire flexible avec des interfaces natives, AXI ou AHB, permettant l’intégration de caches instructions et données et de mémoires fortement couplées pour l’exécution de code critique.

-fr.jpg)