Grâce à des collaborations stratégiques avec notamment les sociétés Samsung Foundry et Arm, le fournisseur américain d’outils de conception Cadence annonce le lancement d'un écosystème de partenaires autour d’une spécification pour l’assemblage de chiplets (*) en vue de concevoir des circuits complexes.

Cet écosystème vise à simplifier l'ingénierie et à accélérer la commercialisation des chiplets destinés aux applications d'IA physique, de centres de données et de calcul haute performance (HPC).

Parmi les premiers partenaires rejoignant Cadence, outre Arm, on trouve les sociétés Arteris, eMemory, M31 Technology, Silicon Creations et Trilinear Technologies, ainsi que proteanTecs, partenaire spécialisé dans l'analyse des semi-conducteurs.

Afin de réduire les risques et de faciliter l'adoption de cette approche, Cadence propose à ce niveau des solutions fondées sur des chiplets "pré-validés" compatibles avec la plateforme Physical AI de la société.

Parallèlement, Cadence collabore avec Samsung Foundry pour développer un prototype de silicium issu de la plateforme de chiplets Physical AI, intégrant des blocs de propriété intellectuelle sous forme de chiplets "pré-intégrés" sur le procédé SF5A de Samsung Foundry.

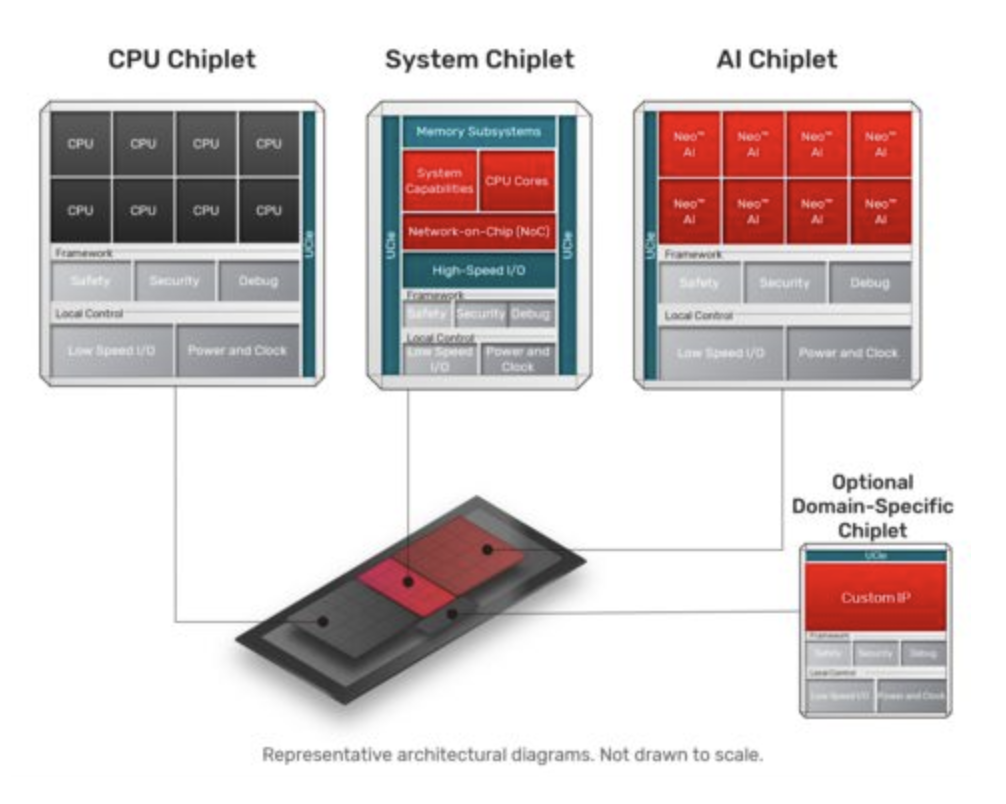

L'écosystème baptisé par Cadence “Chiplets Spec-to-Packaged Parts” s'appuiera dans un premier temps sur le sous-système de calcul avancé Zena d’Arm (CSS, Compute SubSystem) ) et sur d'autres IP essentielles (sans que Cadence ne dévoile lesquelles) pour optimiser sa plateforme de chiplets d'IA physique et son framework de chiplets.

L'écosystème baptisé par Cadence “Chiplets Spec-to-Packaged Parts” s'appuiera dans un premier temps sur le sous-système de calcul avancé Zena d’Arm (CSS, Compute SubSystem) ) et sur d'autres IP essentielles (sans que Cadence ne dévoile lesquelles) pour optimiser sa plateforme de chiplets d'IA physique et son framework de chiplets.

Objectif : répondre aux exigences élevées du traitement de l’IA embarqué de nouvelle génération pour les automobiles, la robotique et les drones, ainsi qu'aux besoins des puces d’entrées/sorties et de mémoire standardisées pour les applications de centres de données, de cloud et de calcul haute performance (HPC).

« Le nouvel écosystème de puces de Cadence représente une étape importante dans le développement des puces électroniques, commente David Glasco, vice-président du groupe Solutions de calcul chez Cadence. Les architectures multi-puces sont devenues essentielles pour optimiser les performances et les coûts face à la complexité croissante des conceptions. Dans ce cadre, la solutions de Cadence à base de chiplets a pour ambition d'apporter une grande flexibilité de personnalisation et une meilleure configurabilité des puces complexes.»

Le flux d'outils de CAO de Cadence permet une simulation fluide avec le simulateur logique Xcelium une émulation avec la plateforme d'émulation d'entreprise Palladium Z3 de la société, tandis que le flux de conception physique exploite un retour d'information en temps réel pour des cycles de placement et de routage efficaces.

Pour rappel, un chiplet est une puce spécialisée conçue pour être combinée à d'autres puces dans un même boîtier, afin que le dispositif final se comporte comme une seule puce. Au lieu de construire un SoC (System On Chip) monolithique, les concepteurs répartissent les fonctions de calcul, d’entrées/sorties, d’interfaces mémoire… puis les assemblent par des liaisons inter-puces à haut débit. L’idée sous-jacente est d’obtenir un meilleur rendement en production, une réutilisation accrue des fonctions unitaires et la possibilité d'intégrer chaque fonction au nœud de gravure le plus adapté.

Dans ce cadre, la proposition de Cadence vise à démocratiser les chiplets en intégrant ses partenaires fournisseurs de blocs d'IP et son expertise en matière d'encapsulation dans un flux conforme à des spécifications liées au design des chiplet.

En d’autres termes, l'idée est de partir d'une spécification de chiplet, d'assembler un framework à partir de blocs d'IP puis d'appliquer un processus d’implantation et vérification reproductible. Et ce en s’appuyant sur des chiplets "pré-validés" (et leur encapsulation) plutôt que sur la simple fourniture d'IP.

A ce niveau, Cadence indique que la complexité des chiplets ne réside pas uniquement dans les puces individuelles, car comme il s’agit d’un processus d’assemblage, il faut vérifier le comportement des interfaces entre puces, l'intégrité du signal du boîtier, l'alimentation et la dissipation thermique. Et de répéter ces vérifications lorsqu'un des blocs constitutif de la puce finale est modifié.

-fr.jpg)