Dans la lignée de l’accord signé avec Western Digital fin 2019, la société allemande d'origine tchèque Codasip a annoncé en juin l’extension de son package de mise en œuvre matérielle des cœurs de processeur RISC-V SweRV de l'Américain aux modèles open source Core EH2 et EL2 ...que Western Digital a récemment versés comme contributions à l’alliance Chips (lire notre article ici). Ces deux IP viennent donc s’ajouter au cœur Core SweRV EH1 déjà pris en charge par Codasip.

On rappellera que l’alliance Chips a pour objectif de développer dans le cadre d’un environnement collaboratif un jeu de blocs d’IP et d’outils open source facilitant la conception de processeurs et de puces-systèmes SoC bâtis sur l’architecture RISC-V. Et ce sur des marchés aussi divers que les terminaux mobiles, l’informatique, l’électronique grand public et l’Internet des objets.

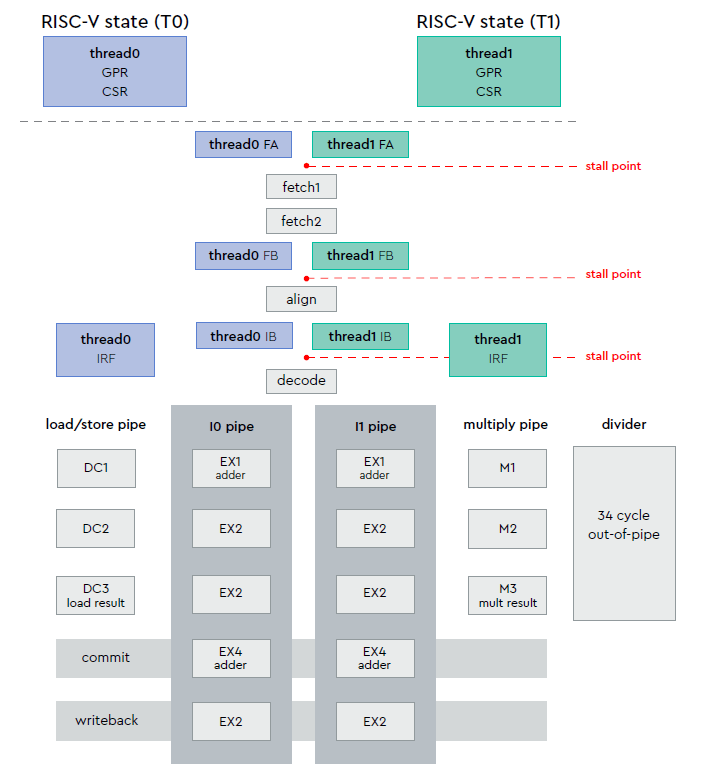

Le SweRV Core EH2 est un cœur 32 bits superscalaire à double thread et pipeline à neuf étages dont les performances peuvent atteindre 6,3 CoreMark/MHz pour une empreinte silicium de 0,067 mm2 une fois gravé en technologie Cmos TSMC 16 nm. Compatible avec le jeu d’instructions RV32IMAC avec extensions de manipulation de bits, il est conçu pour les équipements prenant en charge des applications fortement consommatrices de données dans des domaines comme la périphérie de réseau (edge), l'intelligence artificielle (IA) et l'Internet des objets (IoT).

Le SweRV Core EH2 est un cœur 32 bits superscalaire à double thread et pipeline à neuf étages dont les performances peuvent atteindre 6,3 CoreMark/MHz pour une empreinte silicium de 0,067 mm2 une fois gravé en technologie Cmos TSMC 16 nm. Compatible avec le jeu d’instructions RV32IMAC avec extensions de manipulation de bits, il est conçu pour les équipements prenant en charge des applications fortement consommatrices de données dans des domaines comme la périphérie de réseau (edge), l'intelligence artificielle (IA) et l'Internet des objets (IoT).

Le SweRV Core EL2, quant à lui, est un cœur 32 bits RISC-V très compact à faible consommation doté de performances jusqu’à 3,6 CoreMark/MHz, optimisé pour des applications telles que les séquenceurs de machines d'état et les générateurs de formes d'onde. Il est compatible avec le jeu d’instructions RV32IMC.

Développé par Codasip en coopération avec Western Digital, le package de mise en œuvre matérielle SweRV Support Package fournit un jeu d’outils et de composants nécessaires à la conception, l’implémentation, le test et la programmation logicielle d’une puce-système architecturée autour de cœurs SweRV. Il en existe une version gratuite pour l’enseignement qui inclut la chaine d’outils logicielle, des outils de CAO open source, l’intégration au flot de conception et l’accès à un forum d’utilisateurs. La version Pro fournit l’intégration à des flots de CAO commerciaux ainsi qu’un support client professionnel.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)