Le fabricant de semiconducteurs NXP vient de dévoiler la troisième génération de ses processeurs d'imagerie radar fabriqués en technologie FinFET 16 nm, capables d’offrir une puissance de traitement deux fois supérieure par rapport à la génération précédente.

Les S32R47, c’est leur nom, combinent des émetteurs-récepteurs radar à ondes millimétriques, associés notamment à un système de gestion de l'alimentation optimisé pour répondre aux exigences de sécurité fonctionnelle décrites dans les spécifications ISO 26262 ASIL B.

Selon le rapport "Status of the Radar Industry 2024" réalisé par la société d’analyse de marché Yole Intelligence, d'ici 2029, environ 40 % des véhicules en circulation seront des voitures particulières équipées d'une automatisation de conduite de niveau 2+ (L2+) et de niveau 3 (L3), ainsi qu'un nombre croissant de véhicules de niveau 4 (L4).

Selon NXP, pour répondre aux exigences de ce marché de la conduite autonome pour les véhicules utilitaires légers, les équipementiers automobiles doivent améliorer les performances des radars, une évolution cruciale pour supporter des fonctionnalités d'autonomie sûres, telles que la conduite autonome et le stationnement entièrement automatisé.

« Le processeur S32R47 peut traiter efficacement trois fois plus de canaux d'antenne en temps réel que les offres actuelles sur le marché, et améliore la résolution, la sensibilité et la portée dynamique du radar d'imagerie, requises par les cas d'utilisation exigeants de la conduite autonome, tout en respectant les objectifs stricts de consommation et de coût système fixés par les équipementiers pour la production en série, commente Meindert van den Beld, directeur général, Radar et ADAS chez NXP.

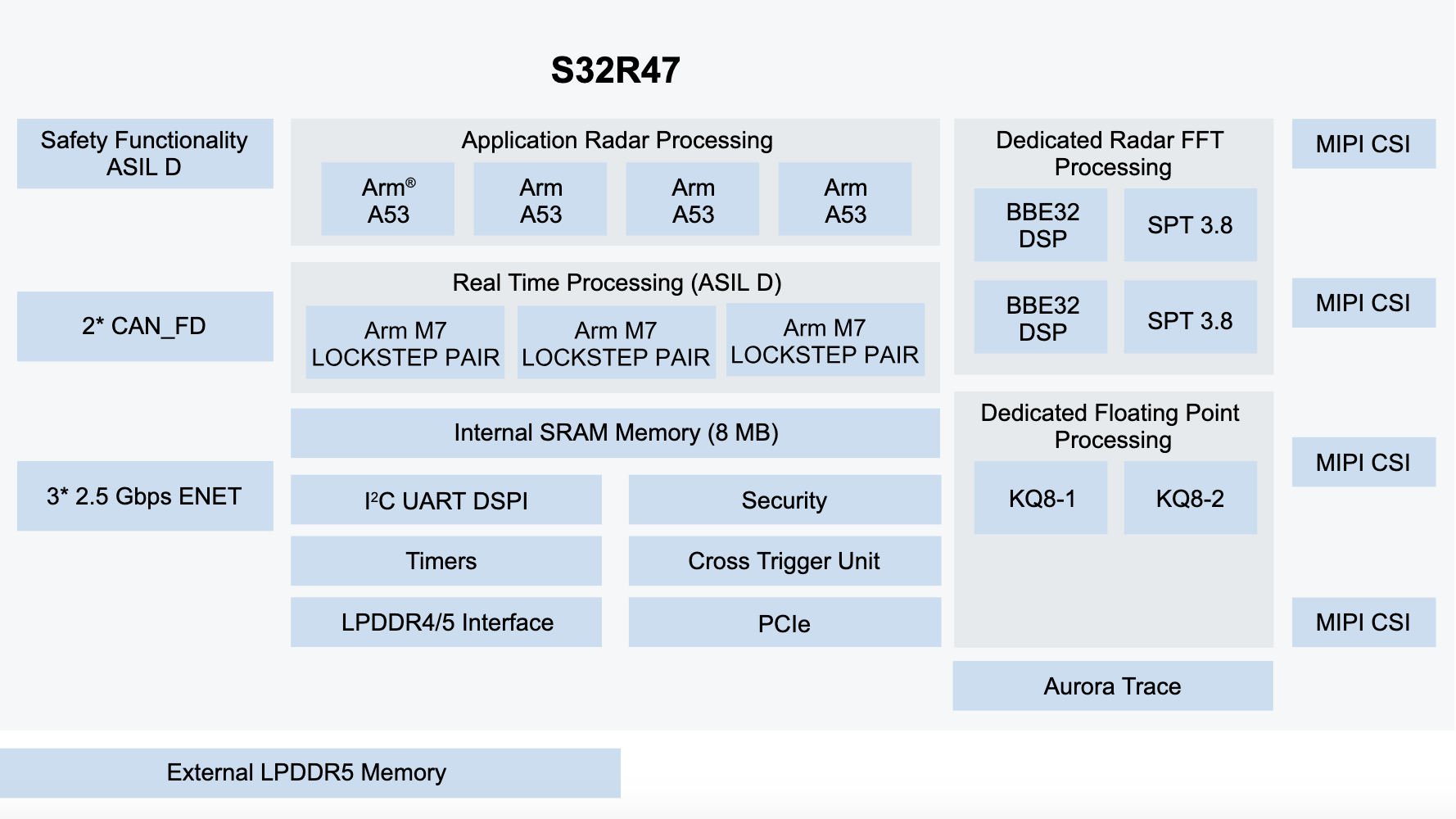

Ce radar d'imagerie est doté de quatre coeurs Arm Cortex-A53 cadencés à 1,2 GHz et de trois coeurs Arm Cortex-M7 cadencés à 400 MHZ avec un mécanisme de lock-step (*) sur ces trois derniers pour atteindre un niveau de sûreté de fonctionnement élevé.

Le circuit est conçu pour gérer des données de nuages de points plus riches pour une modélisation détaillée de l'environnement. Il s'agit d'un élément clé pour les systèmes de perception fondé sur l'IA dont l'objet est de faciliter la conduite assistée et autonome dans des conditions environnementales difficiles, comme les scénarios urbains complexes.

Dans ce cadre, le S32R47 est doté d'un système de traitement radar multicœur autorisant le traitement d’un nuage de points plus dense grâce à des algorithmes de traitement spécifiques compatibles avec les systèmes ADAS de nouvelle génération. Des évolutions qui améliorent notamment la notion de séparabilité des objets, la fiabilité de la détection et la classification plus précise d'éléments tels que les usagers de la route vulnérables ou les marchandises perdues.

S'appuyant sur le savoir-faire et la technologie éprouvée des deux générations de circuits SR32Rxx, le S32R47 procure, selon NXP, des performances de traitement jusqu'à deux fois supérieures au niveau du microprocesseur du radar dans un encombrement réduit de 38 %.

Il prend également en charge des applicaitons d'intelligence artificielle et d'apprentissage automatique (IA/ML) pour des fonctionnalités telles que le traitement amélioré de la direction d'arrivée des ondes radar (DoA, Diection of Arrival) et la classification des objets.

Le S32R47 présenté sous la forme d’un composant BGA de 15 sur 15 mm, fonctionne dans la gamme de température étendue - 40 ºC jusqu’à 150 °C et est conforme à la norme automobile AEC-Q100 Grade-1.

(*) Le lockstep est une technique permettant d'obtenir une fiabilité élevée dans un système à microprocesseur. Plusieurs processeurs identiques, jusqu'à 3, sont initialisés au même état et reçoivent les mêmes entrées en parallèle, exécutant simultanément le même ensemble d'instructions, tout en comparant en permanence leurs résultats. Toute divergence détectée indique alors une erreur potentielle ou un défaut dans l'un des cœurs, déclenchant un mécanisme de gestion des défauts.

-fr.jpg)