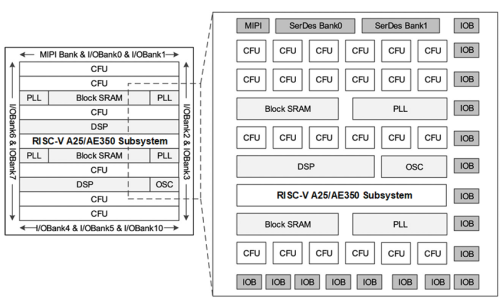

La société Andes Technology, qui est l’un des principaux fournisseurs de cœurs de processeurs RISC-V 32 bits et 64 bits, annonce l’intégration du cœur RISC-V AndesCore A25 et de son sous-système périphérique AE350 dans le silicium de la puce-système FPGA GW5AST-138 du chinois Gowin Semiconductor. Ce qui constituerait une première pour une puce FPGA gravée selon un procédé 22 nm.

Selon Andes, cette intégration fournit aux concepteurs la puissance du cœur A25 et les périphériques dont ont besoin la plupart des processeurs sans consommer de ressources FPGA. Partant, les équipes en charge de la conception matérielle peuvent déployer leur valeur ajoutée dans la matrice FPGA de la puce de Gowin, tandis que les développeurs logiciels peuvent simultanément mettre au point du code applicatif reposant sur l’écosystème RISC-V.

« Dans notre famille Arora V, nous intégrons dans le silicium les périphériques dont un processeur RISC-V a généralement besoin, explique Jim Gao, directeur en charge du développement de solutions chez Gowin. Nous avons ainsi inclus un SerDes haut débit entièrement contrôlable pour les applications de communication, un sous-système d’agrégation vidéo et un bloc d’accélération des traitements IA qui exigent des débits très élevés. Parmi les autres fonctions instanciées dans le silicium, on trouve des modules Block RAM avec correction d'erreur ECC, des GPIO à tensions multiples hautes performances et une architecture d'horloge à haute précision. Ces fonctions matérielles permettent de garder disponible la structure programmable FPGA qui comprend jusqu'à 138 000 tables de correspondances (LUT) pour la mise en œuvre de la logique propre aux concepteurs. »

Dans le détail, le cœur RISC-V AndesCore A25 gravé dans le silicium de la puce-système FPGA GW5AST-138 est cadencé à 400 MHz et prend en charge l'extension P du jeu d’instructions RISC-V DSP/SIMD (actuellement à l’état de projet), les instructions RISC-V à virgule flottante à simple et double précision et de manipulation de bits, ainsi que la MMU (Memory Management Unit) pour les applications Linux. La plate-forme AE350 compatible AXI/AHB, quant à elle, est livrée avec des mémoires de niveau un, un contrôleur d'interruptions, un module de débogage, un contrôleur matriciel de bus AXI et AHB, un pont AXI vers AHB et un ensemble de blocs d’IP fondamentaux du bus AHB/APB préintégrés.

En Europe, les FPGA et puces-systèmes FPGA de Gowin sont notamment disponibles chez les distributeurs Mouser et Rutronik.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)