Nombre élevé d’entrées/sorties, grande efficacité énergétique et fonctions sophistiquées de sécurité, tel est le pedigree des nouveaux FPGA et SoC FPGA de la famille Spartan UltraScale+ d’AMD (d’origine Xilinx) destinés aux applications dans les secteurs de la vision embarquée, de la santé, des réseaux industriels, de la robotique et de la vidéo.

Dans le détail, ces circuits fabriqués en technologie 16 nm affichent une consommation d'énergie totale jusqu'à 30% inférieure à la génération précédente (les FPGA Artix 7 produits en technologie 28 nm) et ce en grande partie grâce à la technologie FinFET 16 nm.

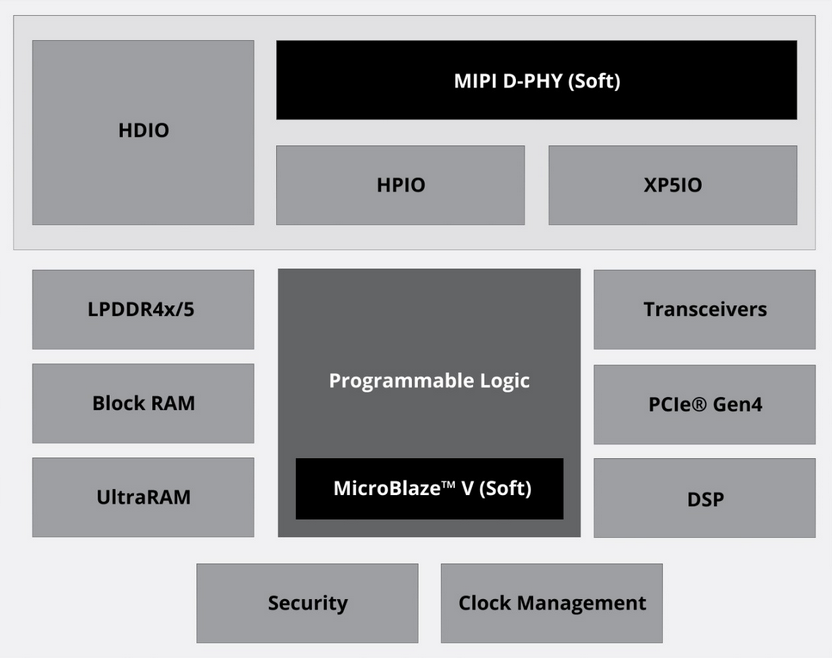

Les Spartan UltraScale+ proposent aux développeurs jusqu’à 572 E/S, 128K de cellules logiques et la capacité à fonctionner sous une tension jusqu'à 3,3 V. Soit, selon AMD, le rapport E/S par cellule logique le plus élevé de l'industrie pour des FPGA gravés avec une technologie inférieure à 28 nm. Au-delà, il s’agit chez AMD des premières puces UltraScale+ dotées d'un contrôleur mémoire LPDDR5 et d’une interface compatible PCle Gen4 x8.

Les Spartan UltraScale+ proposent aux développeurs jusqu’à 572 E/S, 128K de cellules logiques et la capacité à fonctionner sous une tension jusqu'à 3,3 V. Soit, selon AMD, le rapport E/S par cellule logique le plus élevé de l'industrie pour des FPGA gravés avec une technologie inférieure à 28 nm. Au-delà, il s’agit chez AMD des premières puces UltraScale+ dotées d'un contrôleur mémoire LPDDR5 et d’une interface compatible PCle Gen4 x8.

Mais c’est du côté sécurité que se distinguent les FPGA et SoC FPGA Spartan UltraScale+ (les SoC FPGA associent une matrice de logique programmable à un cœur de processeur 32 bits MicroBlaze d’origne Xilinx). Avec notamment le support de la cryptographie post-quantique avec des algorithmes approuvés par l’organisme américain NIST (National Institute of Standards and Technology) pour une protection des blocs de propriété intellectuelle contre les cyberattaques. Les puces se distinguent aussi par l’intégration d’une fonction d'inviolabilité physique qui confère à chaque dispositif une empreinte numérique unique, une prévention de la falsification étant par ailleurs assurée par le biais de clés PPK/SPK (Primary Public Key/Secondary Public Key) qui assurent une gestion des clés de sécurité obsolètes ou compromises. En parallèle, une analyse différentielle de la consommation permet une protection contre les attaques classiques par canaux auxiliaires et un dispositif dit “anti-sabotage” permanent protège contre les utilisations abusives.

Pour le développement d’applications, l'ensemble du portefeuille des FPGA et SoC FPGA d’AMD est pris en charge par l’environnement Vivado Design Suite et par la plate-forme Vitis Unified Software Platform, autorisant les concepteurs de matériels et de logiciels à tirer parti des avantages de productivité respectifs de ces deux outils.