Sous le nom de Tensilica FloatingPoint, l’américain Cadence a développé une nouvelle famille de DSP pour puces-systémes SoC spécifiquement conçus pour les charges de travail exigeantes en calculs en virgule flottante et optimisés en matière de consommation, de performances et d’empreinte silicium.... Déclinée en quatre cœurs (KP1, KP6, KQ7 et KQ8), cette famille a vocation à couvrir un large éventail d’applications, des dispositifs éco-efficaces alimentés sur piles aux systèmes de réalité virtuelle ou augmentée, en passant par l’intelligence artificielle et l’apprentissage automatique (AI/ML), la commande moteur, la fusion de capteurs et le suivi d’objets sur des marchés comme la téléphonie mobile, l’automobile, l’électronique grand public et l’informatique hyperscale.

Dans la pratique, les DSP Tensilica FloatingPoint partagent le même jeu d’instructions (ISA) que l’unité de calcul en virgule flottante vectorielle (VFPU) proposée en option sur les autres familles de DSP Tensilica. L’idée étant de favoriser la portabilité et la réutilisabilité des logiciels, tout en offrant la possibilité pour les concepteurs de transférer toutes les charges de travail en virgule flottante sur les nouveaux DSP pour une meilleure efficacité.

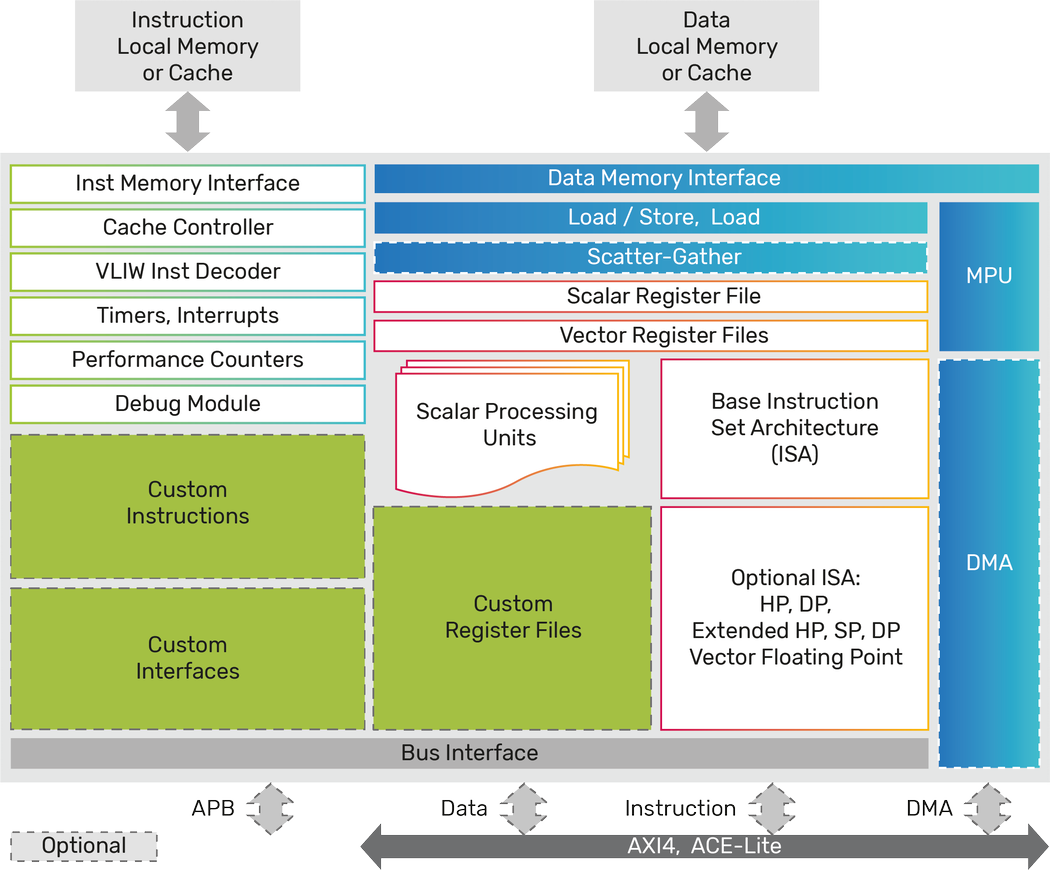

Les DSP Tensilica FloatingPoint, qui s’appuient sur une architecture SIMD (Single Instruction Multiple Data) extensible de 128 bits à 1 024 bits, sont dès aujourd’hui disponibles sur les plates-formes Tensilica Xtensa LX et NX et accélèrent de 25% les opérations FMA (Fused Multiply-Add) par rapport aux DSP Tensilica à virgule fixe dotés de l’option VFPU (Virtual Floating Point Unit), avec à la clé un débit opérationnel plus élevé.

Les DSP Tensilica FloatingPoint, qui s’appuient sur une architecture SIMD (Single Instruction Multiple Data) extensible de 128 bits à 1 024 bits, sont dès aujourd’hui disponibles sur les plates-formes Tensilica Xtensa LX et NX et accélèrent de 25% les opérations FMA (Fused Multiply-Add) par rapport aux DSP Tensilica à virgule fixe dotés de l’option VFPU (Virtual Floating Point Unit), avec à la clé un débit opérationnel plus élevé.

Les performances peuvent en outre être améliorées à l’aide du langage TIE (Tensilica Instruction Extension) à l’instar de tous les processeurs et DSP proposés par Cadence.

En outre, les DSP FloatingPoint permettent de réduire jusqu’à 40% la surface silicium par rapport aux DSP à virgule fixe similaires dotés de l’option VFPU, assure la société américaine.

On notera que les outils logiciels qui accompagnent ces nouveaux DSP disposent d’une fonction d’autovectorisation efficace qui, selon Cadence, permet d’optimiser le code scalaire pour utiliser les unités vectorielles à virgule flottante avec une intervention manuelle minimale, voire nulle.