Il y a tout juste un an, Xilinx avait parcimonieusement donné quelques détails sur les futurs circuits multicœurs programmables de gamme Zynq dits MPSoC (Multi-Processing System on Chip) qui doivent compléter par le haut ...les fameux Zynq-7000, ces composants associant un ou plusieurs cœurs Cortex-A9 à une matrice de FPGA. La société américaine a profité du salon Embedded World 2015 qui ouvre ses portes aujourd’hui 24 février à Nuremberg pour les propulser en pleine lumière.

Xilinx a annoncé officiellement l’échantillonnage d’ici à la fin de l’année des premiers MPSoC d’une nouvelle famille baptisée UltraScale+. Une famille qui comportera aussi des modèles de FPGA de classe Kintex et Virtex et qui pourrait offrir des rapports performances/watt de deux à cinq fois supérieurs à ceux proposés par l’actuelle génération de produits gravés en technologie 28 nm…

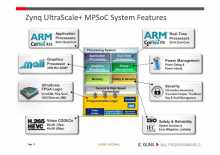

Gravés par TSMC avec une technologie de transistor 3D FinFET à 16 nm, les circuits MPSoC UltraScale+ (voir illustration ci-dessous) associeront de la logique programmable (évidemment…), un processeur quadricœur 64 bits ARM Cortex-A53, un sous-système temps réel à double cœur ARM Cortex-R5 (pour les fonctions nécessitant déterminisme, fiabilité et sûreté de fonctionnement), un moteur de gestion de la sécurité, une unité graphique dédiée ARM Mali-400MP ainsi qu’un codec vidéo H.265 (implémenté dans le bloc de logique programmable) et des interfaces DisplayPort, Mipi et HDMI. Le tout est couplé à une unité de gestion système et de gestion de l’alimentation qui permet, en particulier, d’éteindre dynamiquement des moteurs de traitement non utilisés par l’application.

Evolution de l’architecture UltraScale, instillée par Xilinx dans ses FPGA et SoC depuis le passage au procédé de gravure 20 nm, l’architecture UltraScale+ apporte de nouvelles potentialités aux circuits de l’Américain. L’une d’entre elles est liée à la technologie mémoire dite UltraRAM qui permet d’associer des quantités importantes de mémoire au plus près des moteurs de traitement afin d’améliorer à la fois les performances et les délais de latence. Selon Xilinx, le procédé UltraRAM, utilisable pour embarquer sur la puce jusqu’à 432 Mbit de SRam, garantit un meilleur rapport performance/watt et abaisse la facture matérielle. L’architecture UltraScale+ se distingue également par une technologie dénommée SmartConnect qui permet, en fonction des performances recherchées en débit et en latence, d’optimiser la topologie d’interconnexion des éléments constituants du FPGA ou du SoC tout en minimisant le nombre de blocs logiques utilisés pour réaliser ces mêmes interconnexions. Enfin, Xilinx compte associer dans certains Virtex UltraScale+ la gravure FinFET 3D avec son propre procédé 3D (« 3D-on-3D ») qui permet de juxtaposer dans un même boîtier plusieurs FPGA placés côte à côte en les interconnectant via des trous métallisés enterrés (TSV) pour limiter l’encombrement et la consommation.

Avec sa famille de FPGA et MPSoC UltraScale+, Xilinx cible les équipements pour infrastructures de réseaux mobiles LTE-Advanced et pré-5G, les cartes d’interface ligne pour réseaux filaires aux débits supérieurs à 500 Gbit/s, les systèmes ADAS haut de gamme d’assistance évoluée à la conduite automobile et les équipements de l’Internet des objets industriel aptes à traiter (ou prétraiter) des flux massifs de données.

%20(600x424).jpg)