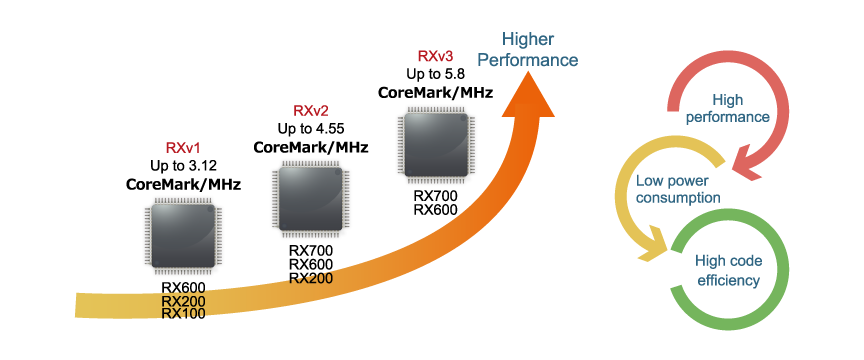

Cinq ans presque jour pour jour après l’annonce de son cœur de processeur 32 bits RXv2, Renesas redonne un coup de fouet à son architecture Cisc propriétaire avec le RXv3. Cette troisième génération du cœur RX sera mise en œuvre dès la fin de cette année ...dans les microcontrôleurs du Japonais et notamment dans les RX600 qui pourront afficher une éco-efficacité de 44,8 CoreMark/mA.

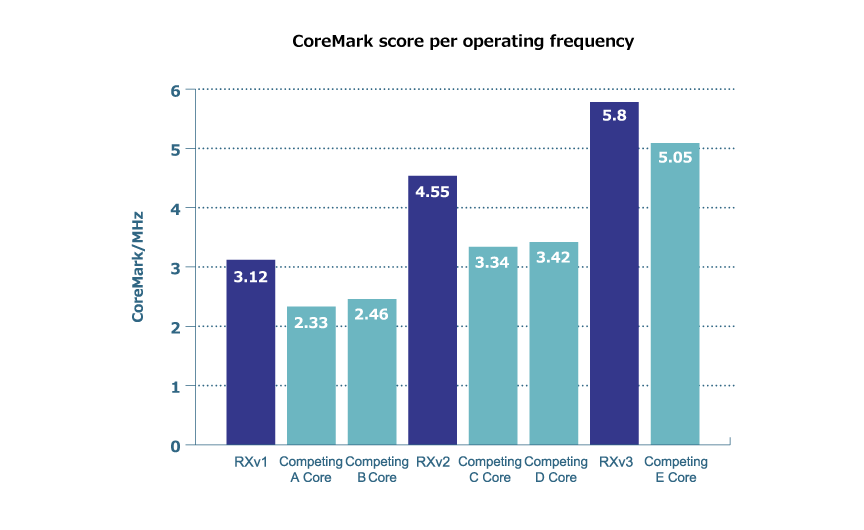

Plus globalement, le cœur RXv3, rétrocompatible avec les générations précédentes RXv1 et RXv2, dope de plus de 25% les performances de l’architecture RX par rapport au RXv2, à hauteur de 5,8 CoreMark/MHz au banc d’essai EEMBC (voir graphique ci-contre). Selon Renesas, les futurs microcontrôleurs RXv3 pourront répondre aux contraintes temps réel et aux exigences de stabilité des applications industrielles et de commande de moteur dans les domaines de la production industrielle, de la maison connectée et des infrastructures intelligentes.

Plus globalement, le cœur RXv3, rétrocompatible avec les générations précédentes RXv1 et RXv2, dope de plus de 25% les performances de l’architecture RX par rapport au RXv2, à hauteur de 5,8 CoreMark/MHz au banc d’essai EEMBC (voir graphique ci-contre). Selon Renesas, les futurs microcontrôleurs RXv3 pourront répondre aux contraintes temps réel et aux exigences de stabilité des applications industrielles et de commande de moteur dans les domaines de la production industrielle, de la maison connectée et des infrastructures intelligentes.

D’un point de vue technique, le cœur RXv3 se déploie selon une architecture superscalaire à cinq étages qui permet au pipeline d’exécuter un plus grand nombre d’instructions simultanément tout en conservant un bon niveau d’éco-efficacité, explique Renesas. Selon le Japonais, les temps de réponse aux interruptions ont également été améliorés grâce à une option de sauvegarde des registres en un seul cycle avec, à la clé, un temps de changement de contexte pour les systèmes d’exploitation temps réel réduit de 20%. Tout comme le RXv2, le cœur RXv3 est apte à effectuer simultanément les opérations DSP et de calcul en virgule flottante en double précision (DSP/FPU) et les accès mémoire pour accélérer les fonctions de traitement du signal.

-fr.jpg)