Sous le nom de Propel, le fournisseur de composants logiques programmables à basse consommation Lattice lance un environnement de conception destiné à accélérer le développement d’applications sur ses FPGA de petites dimensions, et ce via l’assemblage simple et rapide d’éléments issus d’une bibliothèque d’IP, ...dont un cœur de processeur RISC-V et divers blocs périphériques.

Selon la société de semi-conducteurs, les utilisateurs novices de FPGA cherchent des solutions de conception qui soient à la fois flexibles et simples d’usage et qui intègrent tous les logiciels et blocs d’IP nécessaires au développement d’applications innovantes, le tout sans courbe d’apprentissage. Pour répondre à cette attente, l’environnement Lattice Propel intègre des outils de développement qui automatisent une grande partie du processus de conception aussi bien matériel que logiciel au sein d’un framework unique. L’idée étant que les développeurs puissent commencer à créer le logiciel système avant même que le matériel ne soit disponible.

« L'interface utilisateur graphique de Lattice Propel permet aux développeurs sur FPGA novices d’intégrer dans leur conception des blocs d’IP issus de la bibliothèque d’IP de l’environnement par simple glisser-déposer, indique Roger Do, directeur produits de Lattice. L’outil automatise ensuite le layout de la conception pour intégrer les nouvelles IP. Pour les développeurs chevronnés, Propel permet de faire de l'édition par script pour une optimisation plus granulaire ou pour une mise à jour rapide des conceptions existantes afin de les porter sur de futurs systèmes intégrant des FPGA Lattice. »

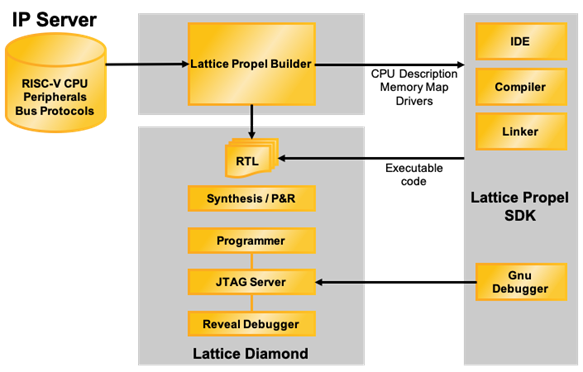

Dans le détail, Lattice Propel se compose de deux éléments, un environnement d’intégration d’IP (Lattice Propel Builder) et un SDK. Le premier, accessible à travers une interface utilisateur graphique et des outils de ligne de commande, offre l’accès à un serveur d’IP régulièrement mis à jour qui, selon Lattice, permet aux développeurs d’implanter en quelques minutes de nouvelles IP sur des conceptions FPGA.

Dans le détail, Lattice Propel se compose de deux éléments, un environnement d’intégration d’IP (Lattice Propel Builder) et un SDK. Le premier, accessible à travers une interface utilisateur graphique et des outils de ligne de commande, offre l’accès à un serveur d’IP régulièrement mis à jour qui, selon Lattice, permet aux développeurs d’implanter en quelques minutes de nouvelles IP sur des conceptions FPGA.

Pour l’heure, le serveur propose huit IP dont un cœur de processeur compatible RISC-V RV32I et divers blocs périphériques (UART, QSPI, I2C, etc.). Pour simplifier l’interconnexion et la gestion des IP dans des systèmes plus complexes, tous les cœurs d'IP disponibles via Lattice Propel Builder sont compatibles avec la spécification d'interconnexion sur puce Amba, précise Lattice. Le SDK Lattice Propel, quant à lui, permet de démarrer le développement logiciel avant que le matériel ne soit disponible. On y trouve des outils de développement standard, des bibliothèques logicielles et des BSP (Board Support Package) de développement permettant de compiler, analyser et déboguer le logiciel applicatif.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-fr.jpg)