Xilinx avec ses modèles ACAP Versal et Intel avec ses Agilex n’ont qu’à bien se tenir. Le concepteur américain de FPGA et de blocs d’IP de logique programmable Achronix compte échantillonner au cours du quatrième trimestre 2019 une nouvelle famille de FPGA censés répondre aux besoins des applications d’intelligence artificielle, ...d’apprentissage automatique et d’accélération de données à très haut débit.

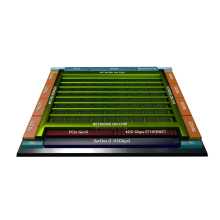

Gravée en technologie FinFET 7 nm par le fondeur TSMC, la famille Speedster7t se distingue par l’intégration d’un réseau 2D de communication sur puce NoC (Network-on-Chip) présenté comme « révolutionnaire » et d’un ensemble à haute densité de processeurs optimisés pour le machine learning (MLP). De quoi, selon Achronix, apporter au marché un composant de classe FPGA+ associant la capacité de programmation du FPGA, les structures de routage des Asic et des moteurs de calcul. Les Speedster7t embarquent également des interfaces mémoire haut débit GDDR6, des ports Ethernet à 400 Gbit/s et des liens PCI Express Gen5, tous interconnectés pour assurer une bande passante de classe Asic, assure la société de semi-conducteurs.

.jpg) « En combinant fonctions mathématiques, mémoire et souplesse de programmation dans ses processeurs MLP et en les associant à une structure bidimensionnelle de réseau-sur-puce à l’échelle du circuit, Achronix a élaboré une manière géniale d’éliminer les goulets d’étranglement et d’assurer un flux sans entraves des données au sein de la puce », s'est enthousiasmé Rich Wawrzyniak, analyse spécialiste des Asic et des puces-systèmes SoC pour Semico Research.

« En combinant fonctions mathématiques, mémoire et souplesse de programmation dans ses processeurs MLP et en les associant à une structure bidimensionnelle de réseau-sur-puce à l’échelle du circuit, Achronix a élaboré une manière géniale d’éliminer les goulets d’étranglement et d’assurer un flux sans entraves des données au sein de la puce », s'est enthousiasmé Rich Wawrzyniak, analyse spécialiste des Asic et des puces-systèmes SoC pour Semico Research.

Dans le détail, les MLP sont étroitement couplés avec des blocs mémoire embarqués afin d’éliminer les délais de latence traditionnellement associés au routage dans les FPGA et de garantir la livraison des données aux MLP à la fréquence maximale de 750 MHz. Du côté des interfaces vers l’extérieur, les Speedster7t sont, dixit Achronix, les seuls FPGA capables aujourd’hui de s’accommoder des mémoires GDDR6.

Avec la présence de 8 contrôleurs GDDR6 aptes à véhiculer chacun un débit de 512 Gbit/s, les plus puissants des derniers-nés d’Achronix peuvent en théorie gérer en cumulé une bande passante GDDR6 de 4 Tbit/s, offrant ainsi une bande passante mémoire équivalente à celle d’un FPGA à interface HBM mais à un coût beaucoup plus faible.

Par ailleurs, les Speedster7t peuvent embarquer jusqu’à 72 SerDes travaillant à un débit compris entre 1 et 112 Gbit/s, des contrôleurs MAC Ethernet 400G avec correction d’erreurs ECC gravés dans le silicium dans des configurations 4x100G ou 8x50G, ainsi que des contrôleurs PCI Express Gen5 également « en dur » avec 8 ou 16 lignes par contrôleur.

Afin d’interconnecter toutes ces interfaces haut débit et d’assurer la communication haut débit entre les moteurs de calcul présents sur la puce, le réseau NoC s’étend horizontalement et verticalement dans la matrice FPGA, chaque rangée ou colonne étant implémentée sous la forme de deux canaux AXI de 256 bits unidirectionnels et capable de délivrer un débit de 512 Gbit/s dans chaque direction simultanément.

Achronix a aussi pensé à la sécurité et a intégré dans la puce plusieurs mécanismes destinés à assurer l’intégrité et la protection des bitstreams. Ceux-ci sont chiffrés et authentifiés via l’algorithme AES-GCM 256 bits et les clés sont elles-mêmes cryptées via une fonction PUF (Physically Unclonable Function). Pour lutter contre les attaques par canaux auxiliaires, les bitstreams sont également segmentés, chaque segment étant chiffré par des clés dérivées indépendamment et le bloc matériel de déchiffrement met en œuvre des contremesures DPA (Differential Power Analysis). Finalement, un protocole d’authentification à clé publique RSA 2048 bits est utilisé pour activer les sous-systèmes matériels de déchiffrement et d’authentification.

La famille Speedster7t se décline en modèles comprenant de 363 000 à 2,6 millions de tables logiques de correspondance LUT à six entrées.