Fruit de la collaboration des fournisseurs d'instruments de mesure Tektronix et Anritsu, une solution de test CEM répondant aux exigences du standard PCIe Gen5 est désormais disponible. L’outil permet la vérification des récepteurs PCIe et le test d’émetteurs et d’horloges de référence.... Cette approche avec une horloge de référence permet notamment de réaliser des tests de préconformité par rapport aux exigences de compatibilité électromagnétique.

Alors que la bande passante du PCI Express double tous les trois ans, la version 5.0 des spécifications de ce bus série haute vitesse autorise des débits jusqu’à 32 gigatransferts/s par lien unidirectionnel. Une valeur qui va encore augmenter puisque l’organisme de standardisation PCI-SIG doit publier en 2021 la spécification PCI Express 6.0 qui portera le débit maximal à 256 Go/s sur 16 liens grâce notamment à la mise en oeuvre de la technologie de modulation d’impulsions en amplitude multiniveaux PAM-4.

Or, avec l’adoption de l’interface PCIe 5.0, de nouvelles problématiques se font jour concernant les procédures de test, en particulier celles qui ont trait à la validation des composants au niveau silicium et le test de conformité CEM selon les spécifications établies par le PCI-SIG. Dans ce cadre, les solutions de test et de débogage PCIe 5.0 de Tektronix permettent de s’assurer que les conceptions répondent aux exigences des nouvelles normes. Le transcepteur PCI Express 5.0 et la solution d’horloge de référence du fabricant répondent aux exigences et aux évolutions des spécifications 5.0 Base, 5.0 CEM et 5.0 Test.

Or, avec l’adoption de l’interface PCIe 5.0, de nouvelles problématiques se font jour concernant les procédures de test, en particulier celles qui ont trait à la validation des composants au niveau silicium et le test de conformité CEM selon les spécifications établies par le PCI-SIG. Dans ce cadre, les solutions de test et de débogage PCIe 5.0 de Tektronix permettent de s’assurer que les conceptions répondent aux exigences des nouvelles normes. Le transcepteur PCI Express 5.0 et la solution d’horloge de référence du fabricant répondent aux exigences et aux évolutions des spécifications 5.0 Base, 5.0 CEM et 5.0 Test.

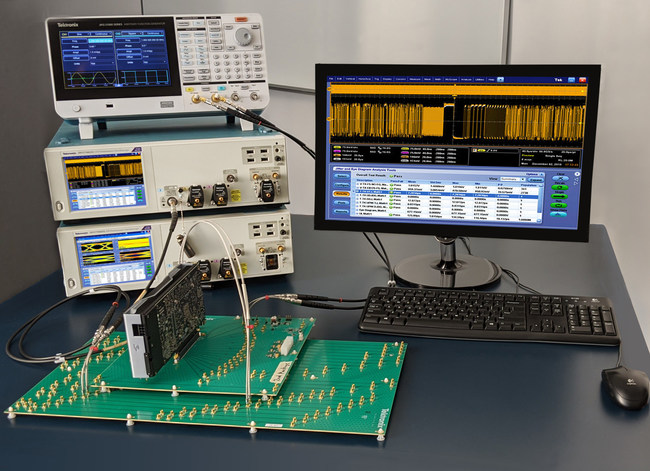

Le système comprend, dans le détail, une solution de test automatique d'émetteurs PCI Express 5.0 (Base & CEM, 32 GT/s) fonctionnant sur un oscilloscope temps réel de la série DPO70000SX et l’analyseur de qualité du signal (BERT) de la gamme MP1900A série R d’Anritsu. Un logiciel de test automatique des récepteurs, développé à cette occasion par Tektronix, exploite des algorithmes d’étalonnage de diagrammes de l’oeil sous les contraintes de débits de 32 et 16 gigatransferts/s.

Au sein du système, plusieurs facteurs de forme (M.2 & U.2) et architectures d’horloge (CC, SRNS, SRIS) sont disponibles. Ce qui permet notamment de suivre l’évolution en temps réel avec la spécification 5.0 Base d’une gigue non corrélée à 32 gigatransferts/s et de réaliser des mesures de gigue de largeur d’impulsion pour minimiser le bruit. Enfin, les technologies mises en œuvre peuvent résoudre les problématiques liées à la gigue d’horloge de référence à 100 MHz et aux mesures d’intégrité du signal grâce à une intégration complète des outils PCIe Clock Jitter de Silicon Labs et DPOJET de Tektronix.