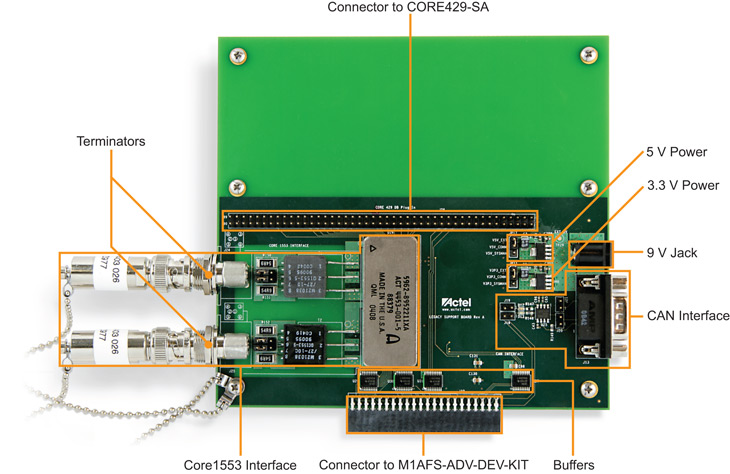

Microsemi certifie ses blocs d’IP de gestion du bus MIL-STD-1553L’américain Microsemi, fournisseur - entre autres - de circuits programmables, poursuit son engagement sur les marchés de la Défense et de l’aérospatial (en partie liés au rachat d’Actel en 2010), en annonçant les évolutions ...de deux blocs d’IP, les Core1553BRT et Core1553BRM, dédiés à la gestion du bus de communication série multiplexé MIL-STD-1553, très largement utilisé en avionique militaire. La version 4.0 de ces deux cœurs de propriété intellectuelle sont désormais certifiés par les Autorités pour les architectures SmartFusion2, circuits intégrés SoC à logique programmable dotés d’un cœur ARM Cortex-M3, et pour les FPGA de la famille Igloo2 de Microsemi. Ces Core1553 de la société supportent les fonctionnalités BC (Bus Controller) pour la gestion de tous les échanges sur le bus, RT (Remote Terminal) pour la gestion des terminaux abonnés utilisant le bus pour communiquer, et MT (Monitor Terminal ou Bus Monitor) pour le suivi des systèmes qui “écoutent” le bus. La version 4.0 ajoute en outre le plan de validation de ces deux cœurs pour la fonction RT (RT Validation Test Plan), tel qu'explicité dans le document MIL-HBDK-1553 Appendice A. Des designs de référence (photo ci-dessous), associés à ces deux blocs d’IP pour les architectures SmartFusion2 et Igloo2, sont également disponibles auprès de Microsemi.

|