L’écosystème bâti autour de l’architecture de processeurs open source RISC-V n’en finit pas de s’étoffer. L’éditeur britannique Imperas Software, spécialiste des plates-formes virtuelles et de simulation logicielle, vient de rejoindre à son tour la fondation RISC-V, créée en 2016 ...et portée par des poids lourds comme Google, Hewlett Packard Enterprise (HPE), IBM, Microsoft, Oracle ou Western Digital. Un organisme où l’on trouve aussi des fournisseurs de blocs d’IP (Andes Technology, Bluespec, Codasip, Cortus, SiFive, UltraSoC, VeriSilicon) ou de composants électroniques (AMD, Espressif, GreenWaves Technology, IDT, Lattice, MediaTek, Micron, Microsemi, Nvidia, NXP, Qualcomm, Rambus, Samsung).

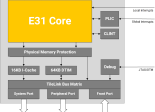

Le ralliement d’Imperas à la fondation RISC-V se cristallise dès aujourd’hui par la disponibilité de modèles et de plates-formes virtuelles ad hoc qui vont permettre le lancement des phases de développement logiciel bien avant que le silicium ne soit effectivement disponible. Dans la pratique, Imperas a développé et publié sur le site Web de l’initiative OVP (Open Virtual Platforms) des modèles en open source des cœurs RISC-V RV32I et RV64I. Selon la firme anglaise, ces modèles, couplés avec d’autres modèles OVP, des API et le simulateur de plates-formes virtuelles OVPsim, permettent la mise au point et la personnalisation de modèles de haut niveau et de plates-formes virtuelles - précis à l’instruction près - de sous-systèmes de SoC, de SoC complets et de systèmes plus complexes dans le cadre de développements logiciels.

Imperas a présenté ses solutions de développement de logiciels embarqués à l’occasion du 6e workshop RISC-V qui s’est tenu du 8 au 11 mai à Shanghai. Elles seront également mises en avant sur le salon DAC (Design Automation Conference) qui ouvrira ses portes du 18 au 22 juin à Austin (Texas).

Pour rappel, l’architecture de processeur RISC-V (à prononcer risk-five) est accessible sous licence BSD et sans paiement de redevances (voir notre article Une alternative open source commence à briller au firmament des architectures de processeurs). Elle définit un jeu d’instructions sur les entiers 32, 64 voire 128 bits, basé sur les principes des architectures matérielles de processeurs Risc (Reduced Instruction Set Computer) tels ARM, Mips, Sparc ou PowerPC. Selon ses promoteurs, les caractéristiques relativement génériques du jeu d’instructions RISC-V, doublées de ses capacités d’extension (avec des instructions d’unité de calcul en virgule flottante par exemple), le rendent adapté aussi bien aux serveurs dans le cloud qu’aux terminaux mobiles ou aux systèmes embarqués les plus contraints. Avec la possibilité de l’implémenter dans des FPGA, des macros synthétisables, des SoC ou des designs intégralement personnalisés.