Un certain nombre de clients d’Intel ont déjà réceptionné des échantillons opérationnels du FPGA Stratix 10 GX 10M, présenté par le géant des semi-conducteurs comme le circuit logique programmable le plus dense du moment avec ses 10,2 millions d’éléments logiques intégrés dans un boîtier de 70 x 74 mm. ...(A des fins de comparaison, le Virtex UltraScale+ VU19P de Xilinx, dévoilé l’été dernier, compte 9 millions d’éléments logiques.)

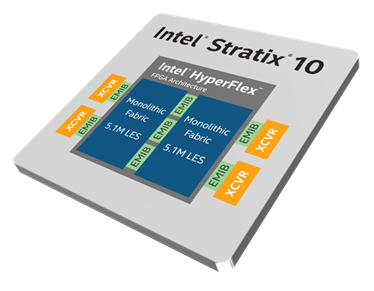

Bâti sur l’architecture Stratix 10, le Stratix 10 GX 10M est le premier FPGA d’Intel à mettre en œuvre la technologie Emib (Embedded Multi-Die Interconnect Bridge) de la firme américaine pour interconnecter deux matrices de logique programmable. Cette technologie ici a permis d’accoler de manière électrique et logique deux dies de matrices monolithiques de Stratix 10 GX (avec une capacité de 5,1 millions d’éléments logiques chacune) avec des briques d’entrées/sorties appropriées.

Bâti sur l’architecture Stratix 10, le Stratix 10 GX 10M est le premier FPGA d’Intel à mettre en œuvre la technologie Emib (Embedded Multi-Die Interconnect Bridge) de la firme américaine pour interconnecter deux matrices de logique programmable. Cette technologie ici a permis d’accoler de manière électrique et logique deux dies de matrices monolithiques de Stratix 10 GX (avec une capacité de 5,1 millions d’éléments logiques chacune) avec des briques d’entrées/sorties appropriées.

Le modèle Stratix 10 GX 10M est approximativement 3,7 fois plus dense que le FPGA Stratix 10 GX 1SG280 qui détenait jusque alors le record de densité dans la gamme de circuits programmables Stratix 10 d’Intel. Il cible plus particulièrement le marché du prototypage et de l’émulation d’Asic, processus qui permettent aux sociétés de semi-conducteurs d’économiser des millions de dollars en contribuant à identifier et à éradiquer des bogues de conception matériels et logiciels avant que les puces ne soient lancées en fabrication.

Ce type de FPGA ultradense peut ainsi servir à développer des algorithmes en utilisant une plate-forme matérielle réelle, de vérifier le fonctionnement de systèmes d’exploitation temps réel, de tester des conditions limites à la fois pour le logiciel et le matériel, d’effectuer des tests de régression sur des itérations successives de la conception ou de démarrer le développement logiciel pour des puces-systèmes SoC avec que les composants ne soient lancés en fabrication.