Lors de la journée virtuelle FPGA Technology Day 2020 organisée le 18 novembre par Intel, la famille des Asic structurés du numéro un des semi-conducteurs - issue du rachat de la société eAsic en 2018 - s’est enrichie avec l’eASIC N5X qui se distingue, pour la première fois à bord de ce type de circuits chez Intel, par la présence de cœurs de processeur à architecture Armv8, ...des Cortex-A53 en l’occurrence.

Rappelons que les Asic structurés sont des architectures matérielles à mi-chemin entre un FPGA, entièrement programmable mais affichant une consommation relativement élevée, et un Asic, dont le fonctionnement est fixé une fois pour toutes dès qu’il sort de chez le fondeur mais dont l'éco-efficacité est très élevée. Les Asic structurés ont pour particularité d’être en partie programmable “en dur” à travers des jeux de masques prédéfinis tout en conservant une optimisation des performances énergétiques avec en sus des temps de développement plus courts que les Asic.

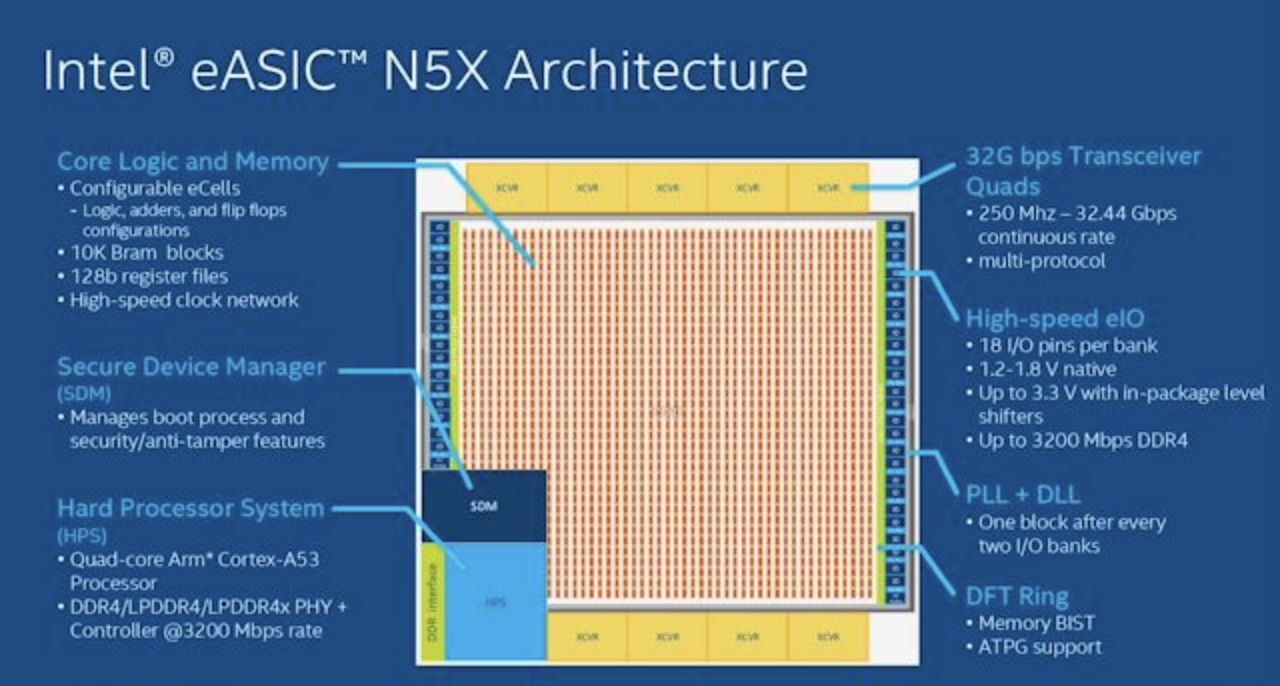

Avec les eASIC N5X (il en existe cinq modèles), Intel propose donc une structure à quatre cœurs Cortex-A53 en dur,avec comme objectif d’aider les concepteurs à développer des solutions personnalisées plus rapidement qu’avec un Asic, pour un coût moins élevé, pour les domaines de la 5G, de l'intelligence artificielle (IA) et des serveurs de données en périphérie de réseau (edge computing).

Dans le détail, le circuit, fabriqué dans un processus TSMC en 16 nm, offre jusqu’à 8,8 millions de portes Asic équivalentes, 229 Mo de mémoire à double port et 20 Mo de fichiers de registre, des émetteurs-récepteurs haute vitesse (jusqu'à 80 à 32,44 Gbit/s) et un gestionnaire de périphériques sécurisé pour les fonctions d'activation, de sécurité et d’antisabotage. A noter que l’eASIC N5X dispose de nombreuses fonctionnalités similaires à celles que l’on retrouve dans le FPGA Agilex d’Intel, une structure innovante dotée justement d’un gestionnaire de périphériques sécurisé et d'un sous-système processeur en "dur".

Parallèlement, lors de cette conférence virtuelle, Intel a présenté l’infrastructure matérielle/logicielle Open FPGA, disponible en open source, dotée de pilotes Linux, et qui s’apparente à une conception de référence pour faciliter le travail de développement sur l’eAsic. Dans cette plate-forme un moteur d'accélération programmable ouvert (OPAE, Open Programmable Acceleration Engine) est disponible (sous la forme d'une pile logicielle provenant de l’écosystème Xeon) ainsi que des exemples d'applications.