Annoncée hier 2 avril 2019 comme une nouvelle ligne de circuits logiques programmables en termes de technologie, la famille des FPGA Agilex d’Intel vise à fournir des solutions personnalisables pour faire face aux défis des applications centrées sur la gestion de flux massif de données... dans les fermes de serveurs ou les équipements réseau, y compris les solutions de périphérie de réseau (edge) toujours plus gourmandes en bande passante et toujours plus sollicitées pour gérer du trafic de données en temps réel.

Selon Intel, qu'il s'agisse d'analyse en périphérie de réseau pour un traitement à faible temps de latence, de fonctions réseau virtualisées pour améliorer les performances, ou d'accélération des traitements au sein des centres de données pour plus d'efficacité, les FPGA Agilex sont conçus pour fournir des solutions pour des applications s'étageant de l’“edge au cloud”.

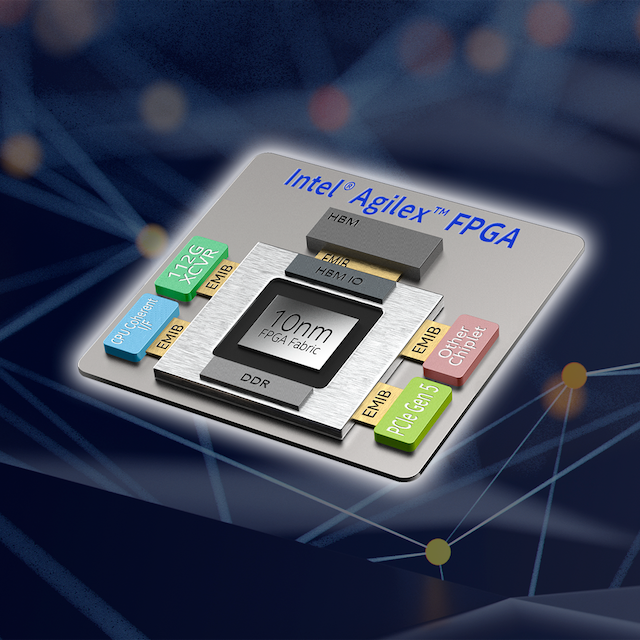

Présentée comme unique en son genre, la famille Agilex associe une structure de FPGA classique conçue pour le procédé de gravure à 10 nm d’Intel à une technologie de type boîtier-système SiP (System In Package) avec une structure 3D hétérogène. Une approche qui permet, selon le géant des semi-conducteurs, d'intégrer dans un seul boîtier une “mosaïque” (chiplet) de périphériques analogiques, de mémoires (DDR5, HBM...), d'unités de traitement maison et d'entrées/sorties personnalisées qui cohabitent avec des blocs technologiques propriétaires eASIC et la matrice de portes du FPGA.

R appelons que à la technologie eASIC, acquise par Intel lors du rachat de la société eASIC en 2018, permet de convertir des fonctions spécialisées en blocs matériels de type Asic (on parle d'Asic structurés) intégrés directement dans le FPGA, afin d’atteindre des performances élevées et des consommations réduites.

appelons que à la technologie eASIC, acquise par Intel lors du rachat de la société eASIC en 2018, permet de convertir des fonctions spécialisées en blocs matériels de type Asic (on parle d'Asic structurés) intégrés directement dans le FPGA, afin d’atteindre des performances élevées et des consommations réduites.

Intel propose donc pour les composants programmables Agilex un continuum logique via des IP réutilisables qu'il est possible de faire migrer de la matrice FPGA vers les cœurs eASIC. Une API logicielle unique fournit en outre pour cette architecture un environnement de programmation permettant aux développeurs d’accéder aux caractéristiques propres au FPGA, mais aussi aux blocs d’accélération matérielle eASIC.

Ainsi, selon Intel, les développeurs peuvent explorer différentes implantations d'une conception parmi différents choix matériels (CPU, FPGA, blocs d’accélération matérielle) afin d’analyser les compromis à faire entre consommation et performances et de choisir l’architecture matérielle/logicielle qui répond le mieux aux besoins.

Dans le détail, les FPGA Agilex prennent en charge Compute Express Link, une technologie d'interconnexion de cache et de mémoire vers les futurs processeurs Xeon Scalable d’Intel (ce qui, on peut le supposer, préfigure l’arrivée à terme de cœurs Xeon au sein de matrices de FPGA).

Grâce à l’architecture HyperFlex de 2e génération (circuit logique accéléré au sein de regstres spécifiques) mise en œuvre sur ce circuit, les performances sont améliorées jusqu'à 40%, et la consommation réduite en parallèle de 40%, par rapport aux FPGA Stratix 10, toujours selon Intel.

Quant aux blocs de DSP des Agilex, ils sont capables de délivrer jusqu’à 40 téraflops de puissance de calcul.

Enfin, côté interconnexion, l’Agilex gère le PCI Express Gen 5 et les émetteurs-récepteurs du circuit (les blocs SerDes) s'accommodent de débits de données pouvant atteindre 112 Gbit/s (Achronix vient de faire une annonce similaire sur ce sujet, voir ici).