La société française Logic Design Solutions étend son portefeuille de blocs d’IP pour la gestion du protocole de stockage NVMe (Non-Volatile Memory express) avec une solution adaptée au FPGA PolarFire de Microchip, doté ici en outre d’un cœur de processeur RISC-V.... Objectif : permettre aux concepteurs de cibler les marchés spécifiques du stockage embarqué avec la technologie NVMe, initialement utilisée sur les marchés des serveurs et des équipements grand public.

Rappelons que le NVMe (dont la spécification a été publiée en 2012) est un protocole de stockage conçu pour les disques à semi-conducteurs et qui fonctionne au-dessus du bus PCI Express (PCIe). Alors que les protocoles traditionnels tels que le SATA ont été élaborés pour les disques magnétiques rotatifs, le NVMe a été créé pour tirer parti de l'enregistrement des données sur mémoire flash en exploitant notamment l’accès aléatoire de ce type de stockage. Ainsi les disques PCIe/NVMe ont la capacité de gérer plusieurs liens PCIe, autorisant des vitesses d'enregistrement supérieures à celle du SATA.

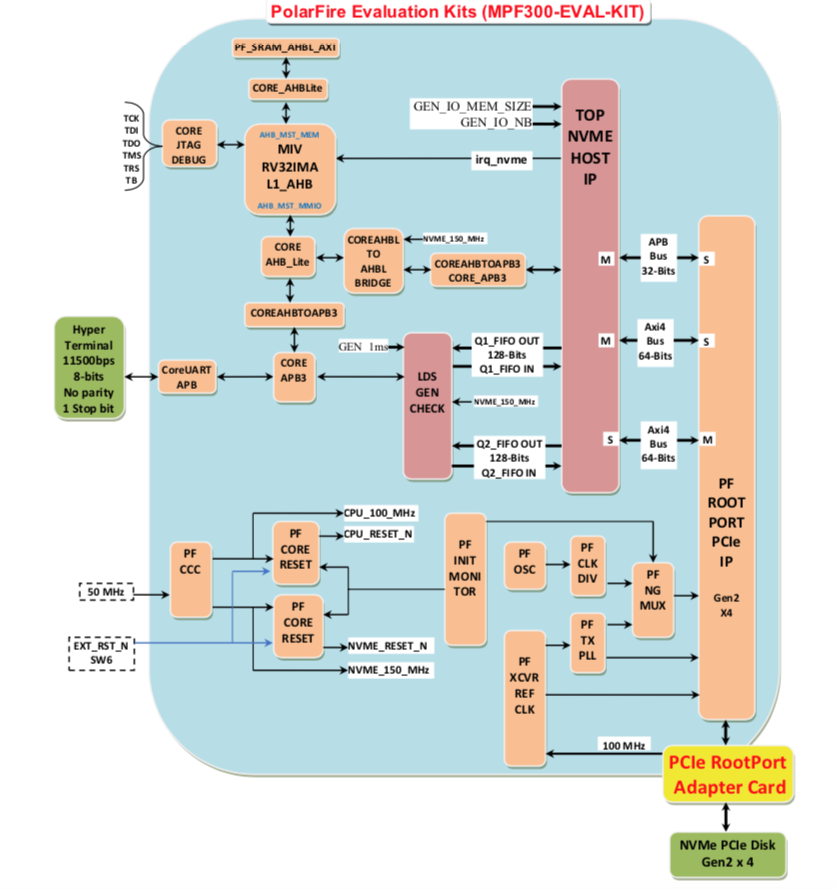

Grâce à son expertise dans le domaine de l'enregistrement embarqué, Logic Design Solutions propose dans ce cadre une IP NVMe hôte, utilisable aussi bien pour ceux qui démarrent dans le domaine des disques NVMe que pour les plus expérimentés. Avec cette solution, tout le protocole NVMe est géré par l’IP, celle-ci étant connectée à une IP PCIe “Root Port” embarquée en dur dans le FPGA. La configuration du PCIe et du NVMe se fait automatiquement à la mise sous tension ou à la demande, après une procédure d'extinction du disque.

Quant à la configuration de la session d'enregistrement, elle se fait en écrivant dans des registres de l'IP, à l'aide d'un bus APB (Advanced Peripheral Bus) spécifié par Arm. Tous les autres bus de données utilisent la spécification AXI4 (Advanced eXtensible Interface 4), la quatrième génération de l’interface Amba d’Arm. De ce fait, le bloc d’IP est gérable soit par une machine à états, dont le code source VHDL est fourni, soit par une CPU dont le code C est également fourni.